#### The SFRA: A Fixed Frequency FPGA Architecture

by

Nicholas Croyle Weaver

B.A. (University of California at Berkeley) 1995

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

**Computer Science**

in the

### GRADUATE DIVISION of the UNIVERSITY of CALIFORNIA at BERKELEY

Committee in charge:

Professor John Wawrzynek, Chair Professor John Kubiatowicz Professor Steven Brenner

2003

The dissertation of Nicholas Croyle Weaver is approved:

Chair

Date

Date

Date

University of California at Berkeley

2003

### The SFRA: A Fixed Frequency FPGA Architecture

Copyright 2003 by Nicholas Croyle Weaver

#### Abstract

The SFRA: A Fixed Frequency FPGA Architecture

by

Nicholas Croyle Weaver Doctor of Philosophy in Computer Science University of California at Berkeley Professor John Wawrzynek, Chair

Field Programmable Gate Arrays (FPGAs) are synchronous digital devices used to realize digital designs on a programmable fabric. Conventional FPGAs use design dependent clocking, so the resulting clock frequency is dependent on the user design and the mapping process.

An alternative approach, a Fixed-Frequency FPGA, has an intrinsic clock rate at which all designs will operate after automatic or manual modification. Fixed-Frequency FPGAs offer significant advantages in computational throughput, throughput per unit area, and ease of integration as a computational coprocessor in a system on a chip. Previous Fixed-Frequency FPGAs either suffered from restrictive interconnects, application restrictions, or issues arising from the need for new toolflows.

This thesis proposes a new interconnect topology, a "Corner Turn" network, which maintains the placement properties and upstream toolflows of a conventional FPGA while allowing efficient, pipelined, fixed frequency operation. Global routing for this topology uses efficient, polynomial time heuristics and complete searches. Detailed routing uses channel-independent packing.

C-slow retiming, a process of increasing the throughput by interleaving independent streams of execution, is used to automatically modify designs so they operate at the array's intrinsic clock frequency. An additional C-slowing tool improves designs targeting conventional FPGAs to isolate the benefits of this transformation from those arising from fixed frequency operation. This semantic transformation can even be applied to a microprocessor, automatically creating an interleaved multithreaded architecture.

Since the Corner Turn topology maintains conventional placement properties, this thesis defines a Fixed-Frequency FPGA architecture which is placement and tool compatible with Xil-

inx Virtex FPGAs. By defining the architecture, estimating the area and performance cost, and providing routing and retiming tools, this thesis directly compares the costs and benefits of a Fixed-Frequency FPGA with a commercial FPGA.

Professor John Wawrzynek Dissertation Committee Chair To my grandparents, who made this all possible.

## Contents

| List of Figures |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of [         | Tables                                                                                                      | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Intr            | oduction                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1             | What are FPGAs?                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2             | Why FPGAs as Computational Devices?                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3             | Why Fixed-Frequency FPGAs?                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.4             | Why the SFRA?                                                                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 1.4.1 Why a Corner-Turn Interconnect?                                                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 1.4.2 Why <i>C</i> -slow Retiming?                                                                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 1.4.3 The Complete Research Toolflow                                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                                                                                                             | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.5             | Overview of Thesis                                                                                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rela            | ated Work                                                                                                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1             | FPGAs                                                                                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.1.1 Unpipelined interconnect, variable frequency                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.1.2 Unpipelined Interconnect Studies                                                                      | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.1.3 Pipelined Interconnect, Variable Frequency                                                            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.1.4 Pipelined, fixed frequency                                                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2             | FPGA Tools                                                                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.2.1 General Placement                                                                                     | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.2.2 Datapath Placement                                                                                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.2.3 Routing                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2.2.4 Retiming                                                                                              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ben             | chmarks                                                                                                     | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1             |                                                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2             | Smith Waterman                                                                                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3             |                                                                                                             | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.4             |                                                                                                             | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.5             | Summary                                                                                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | st of '<br>Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Rela<br>2.1<br>2.2<br>Ben<br>3.1<br>3.2<br>3.3<br>3.4 | st of Tables         Introduction         1.1 What are FPGAs?         1.2 Why FPGAs as Computational Devices?         1.3 Why Fixed-Frequency FPGAs?         1.4 Why the SFRA?         1.4.1 Why a Corner-Turn Interconnect?         1.4.2 Why C-slow Retiming?         1.4.3 The Complete Research Toolflow         1.4.4 This Work's Contributions         1.5 Overview of Thesis         2.1 FPGAs         2.1.1 Unpipelined interconnect, variable frequency         2.1.2 Unpipelined Interconnect Studies         2.1.3 Pipelined Interconnect, Variable Frequency         2.1.4 Pipelined, fixed frequency         2.1.5 Overview of Thesis         2.1 FPGAs         2.1.1 Unpipelined Interconnect, variable frequency         2.1.2 Unpipelined Interconnect, Variable Frequency         2.1.3 Pipelined Interconnect, Variable Frequency         2.1.4 Pipelined, fixed frequency         2.2.1 General Placement         2.2.2 Datapath Placement         2.2.3 Routing         2.2.4 Retiming         3.1 AES Encryption         3.2 Smith Waterman         3.3 Synthetic microprocessor datapath         3.4 LEON Synthesized SPARC core |

| Ι | The                                                            | SFRA Architecture                                                                                                                                                                                                                   | 32                                                                                                                     |

|---|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 4 | <b>The</b> 4.1 4.2                                             | Corner-Turn FPGA Topology         The Corner-Turn Interconnect         Summary                                                                                                                                                      | <b>34</b><br>34<br>38                                                                                                  |

| 5 | <b>The</b> 5.1 5.2 5.3                                         | SFRA: A Pipelined, Corner-Turn FPGA The SFRA Architecture                                                                                                                                                                           | <b>39</b><br>39<br>43<br>44                                                                                            |

| 6 | Reti                                                           | ming Registers                                                                                                                                                                                                                      | 45                                                                                                                     |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                  | Input Retiming                                                                                                                                                                                                                      | 45<br>46<br>48<br>48<br>50<br>51<br>51                                                                                 |

| 7 | The                                                            | Layout of the SFRA                                                                                                                                                                                                                  | 52                                                                                                                     |

|   | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ul> | Layout Strategy         7.1.1       SRAM Cell         7.1.2       Output Buffers         7.1.3       Input Buffers         7.1.4       Interconnect Buffers         Overall Area       Timing Results         Summary       Summary | 52<br>55<br>57<br>58<br>59<br>60<br>61<br>61                                                                           |

|   |                                                                | •                                                                                                                                                                                                                                   | 01                                                                                                                     |

| 8 |                                                                | ting a Corner-Turn Interconnect                                                                                                                                                                                                     | <b>63</b>                                                                                                              |

|   | 8.1<br>8.2                                                     | Interaction with Retiming                                                                                                                                                                                                           | <ul> <li>64</li> <li>64</li> <li>65</li> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>68</li> <li>69</li> </ul> |

|   | 8.3                                                            | Routing Quality & Analysis       8.3.1         AES       8.3.2         Smith/Waterman       8.3.3         Synthetic Microprocessor Datapath       8.3.4         Leon 1       8.3.4                                                  | 69<br>69<br>71<br>72<br>74                                                                                             |

|   | 8.4                                                            | 8.3.4 Leon 1                                                                                                                                                                                                                        | 74<br>75                                                                                                               |

v

| 9  | Other Implications of the Corner-Turn Interconnect       | 76  |

|----|----------------------------------------------------------|-----|

|    | 9.1 Defect Tolerance                                     | 76  |

|    | 9.2 Memory Blocks                                        | 78  |

|    | 9.3 Hardware Assisted Routing                            | 79  |

|    | 9.4 Heterogeneous channels                               | 80  |

|    | 9.5 Summary                                              | 80  |

|    |                                                          |     |

| II | Retiming                                                 | 81  |

| 10 | Retiming, C-slow Retiming, and Repipelining              | 83  |

|    | 10.1 Retiming                                            | 84  |

|    | 10.2 Repipelining                                        | 87  |

|    | 10.3 C-slow Retiming                                     | 88  |

|    | 10.4 Retiming for Conventional FPGAs                     | 90  |

|    | 10.5 Retiming for Fixed Frequency FPGAs                  | 91  |

|    | 10.6 Previous Retiming Tools                             | 93  |

|    | 10.7 Summary                                             | 94  |

| 11 | Applying C-Slow Retiming to Microprocessor Architectures | 95  |

|    | 11.1 Introduction                                        | 95  |

|    | 11.2 <i>C</i> -slowing a Microprocessor                  | 96  |

|    | 11.2.1 Register File                                     | 98  |

|    | 11.2.2 TLB                                               | 99  |

|    | 11.2.3 Caches and Memory                                 | 99  |

|    |                                                          | 100 |

|    |                                                          | 100 |

|    | -                                                        | 101 |

|    |                                                          | 101 |

|    | •                                                        | 101 |

|    | 1                                                        | 101 |

|    |                                                          | 102 |

|    |                                                          | 100 |

| 12 | The Effects of Placement and Hand C-slowing              | 104 |

|    | 12.1 The Effects of Hand Placement and C-slow Retiming   | 104 |

|    | 12.2 AES Results                                         | 106 |

|    | 12.3 Smith/Waterman results                              | 107 |

|    | 12.4 Synthetic Datapath Results                          | 108 |

|    | 12.5 Summary                                             | 109 |

| 13 | Automatically Applying C-Slow Retiming to Xilinx FPGAs   | 110 |

|    | • • • • • •                                              | 110 |

|    |                                                          | 112 |

|    |                                                          | 115 |

|    |                                                          | 116 |

|     | 13.3       | .2 Smith/Waterman                                                                                                             |     |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|     |            | 3.3 Synthetic Datapath                                                                                                        | 120 |

|     |            | .4 LEON 1                                                                                                                     | 120 |

|     | 13.4 Arch  | hitectural Recommendations for the Xilinx                                                                                     | 121 |

|     | 13.5 Retir | ming for the SFRA                                                                                                             | 121 |

|     | 13.6 Sum   | nmary                                                                                                                         | 122 |

|     |            |                                                                                                                               |     |

| III | Compa      | arisons, Reflections and Conclusions                                                                                          | 123 |

| 14  | Comparin   | ng the SFRA with the Xilinx Virtex                                                                                            | 125 |

|     | 14.1 Bend  | chmark Designs                                                                                                                | 125 |

|     | 14.2 The   | SFRA Target                                                                                                                   | 126 |

|     | 14.3 The   | Xilinx Target                                                                                                                 | 126 |

|     | 14.4 Tool  | Iflow Comparisons                                                                                                             | 127 |

|     | 14.5 Thro  | bughput Comparisons without C-slowing                                                                                         | 129 |

|     | 14.6 Thro  | bughput Comparisons with C-slowing                                                                                            | 131 |

|     | 14.7 Late  | ency Comparisons                                                                                                              | 132 |

|     |            | mary                                                                                                                          | 133 |

| 15  | I atonev a | and Throughput: Is Fixed-Frequency a Superior Approach?                                                                       | 134 |

| 15  | •          | Limits of Parallelism                                                                                                         |     |

|     |            | ency and Cryptography                                                                                                         |     |

|     |            | ency and Eixplography                                                                                                         | 130 |

|     |            | ido-Fixed-Frequency FPGA tools                                                                                                |     |

|     |            | ommendations & Conclusions                                                                                                    |     |

|     | 13.3 Kee   |                                                                                                                               | 139 |

| 16  | Open Que   | estions                                                                                                                       | 141 |

|     | 16.1 Pow   | rer Consumption and $C$ -slowing $\ldots \ldots \ldots$ | 141 |

|     | 16.2 Corr  | ner-Turn Interconnect and Coarse-Grained FPGAs                                                                                | 143 |

|     | 16.3 Dep   | opulated C-boxes                                                                                                              | 143 |

|     | 16.4 Sum   | mary                                                                                                                          | 144 |

| 17  | Conclusio  | )n                                                                                                                            | 145 |

|     | 17.1 Bend  | chmark Selection                                                                                                              | 146 |

|     | 17.2 The   | SFRA                                                                                                                          | 147 |

|     | 17.2       | .1 Corner Turn Interconnect and Fast Routing                                                                                  | 147 |

|     |            | 2.2 Compatibility                                                                                                             | 147 |

|     |            | .3 Fixed Frequency Operation                                                                                                  | 148 |

|     |            | owing and Retiming                                                                                                            | 149 |

|     |            | lications to Commercial Products                                                                                              | 150 |

| D:I | bliography | ,                                                                                                                             | 152 |

| DI  | mography   |                                                                                                                               | 134 |

viii

| A | Case        | Study: AES Encryption                  | 160 |

|---|-------------|----------------------------------------|-----|

|   | A.1         | Introduction                           | 161 |

|   | A.2         | The AES Encryption Algorithm           | 162 |

|   | A.3         | Modes of Operation                     | 163 |

|   | A.4         | Implementing Block Ciphers in Hardware | 164 |

|   | A.5         | Implementing AES in Hardware           | 166 |

|   | A.6         | AES Subkey Generation                  | 167 |

|   | A.7         | AES Encryption Core                    | 168 |

|   | A.8         | Testing                                | 169 |

|   | A.9         | Performance                            | 170 |

|   | A.10        | Other implementations                  | 170 |

|   | A.11        | Reflections                            | 172 |

|   | A.12        | Summary                                | 173 |

| B | Othe        | er Multithreaded Architectures         | 174 |

|   | <b>B</b> .1 | Previous Multithreaded Architectures   | 174 |

|   | B.2         | Synergistic and interference effects   | 176 |

# **List of Figures**

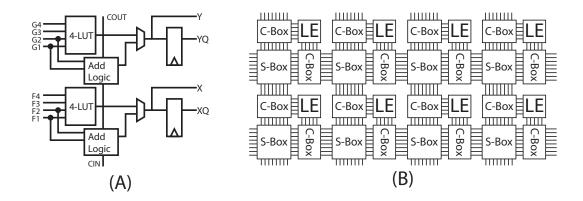

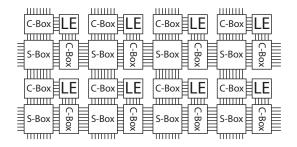

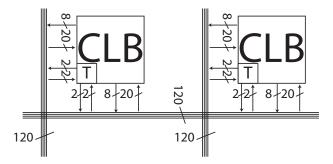

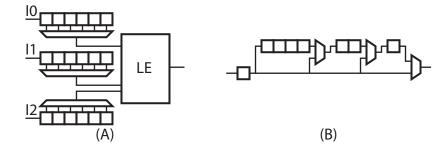

| 1.1        | (A) A simplified FPGA Logic Element (LE) consisting of two 4-input lookup tables (4-LUTs), dedicated arithmetic logic, and 2 flip-flops and (B) The classical components of a Manhattan FPGA: the LE (logic element) performs the computation, the C-box (connection box) connects the LE to the interconnect, and the S-box (switch box) provides for connections within the interconnect.                                                                                                                       | 2        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

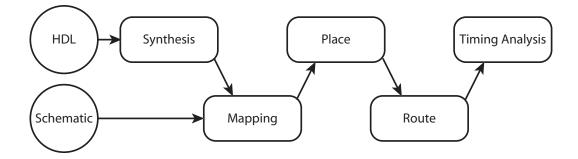

| 1.2        | A typical FPGA CAD flow. User designs are entered either as schematics or in a high level description language (HDL). These designs are first <b>synthesized</b> to create a netlist, which is then <b>mapped</b> onto the FPGA logic elements. These elements are then <b>placed</b> on the array, the connections between the elements are <b>routed</b> , and the final design undergoes <b>timing analysis</b>                                                                                                | 3        |

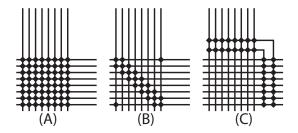

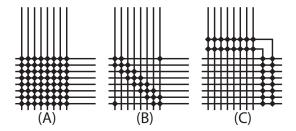

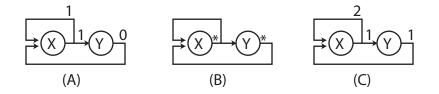

| 1.3        | (A) A crossbar switch-box. (B) A physically-depopulated crossbar. (C) A capacity-<br>depopulated crossbar.                                                                                                                                                                                                                                                                                                                                                                                                        | 8        |

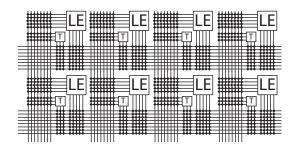

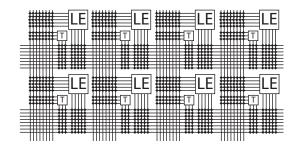

| 1.4        | A corner-turn FPGA interconnect. The C-boxes are implemented as full crossbars, while the S-boxes use capacity-depopulated crossbars to create corner turns, marked                                                                                                                                                                                                                                                                                                                                               | -        |

|            | as T-boxes on this illustration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8        |

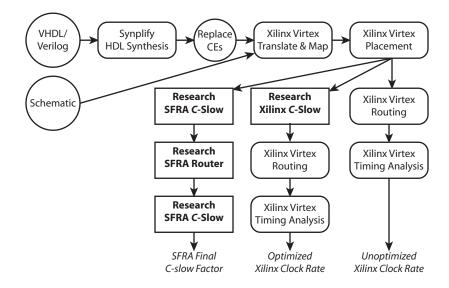

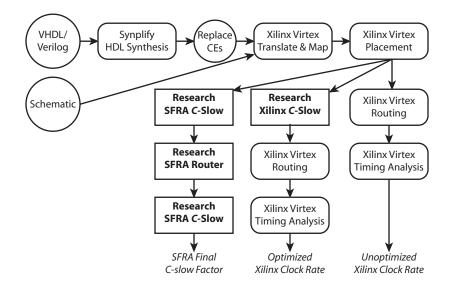

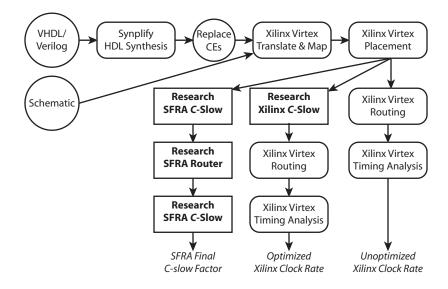

| 1.5        | The complete toolflow created for this research. HDL designs are synthesized with Synplify, then mapped and placed using the Xilinx placement tool. At this point, one of three flows can take place. Either the default Xilinx flow can be invoked to route and perform a timing analysis. Or the designs can be passed through the research $C$ -slow tool (described in Chapter 13) to improve the Xilinx designs. The final option is to $C$ -slow and route for the SFRA. The tools in bold were created for |          |

|            | this thesis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10       |

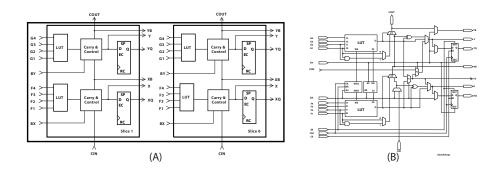

| 2.1<br>2.2 | A Virtex CLB, and the details of a single CLB-slice, from the Xilinx Datasheet [82]. The Stratix Logic Element (LE), from the Stratix datasheet[4]                                                                                                                                                                                                                                                                                                                                                                | 15<br>17 |

| 3.1        | Layout of an individual systolic cell for the Smith/Waterman sequence matching computation                                                                                                                                                                                                                                                                                                                                                                                                                        | 27       |

| 4.1        | The classical components of a Manhattan FPGA: the LE (logic element) performs the computation, the C-box (connection box) connects the LE to the interconnect,                                                                                                                                                                                                                                                                                                                                                    |          |

| 4.2        | and the S-box (switch box) provides for connections within the interconnect (A) A crossbar switch-box. (B) A physically depopulated crossbar. (C) A capacity-                                                                                                                                                                                                                                                                                                                                                     | 34       |

|            | depopulated crossbar.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35       |

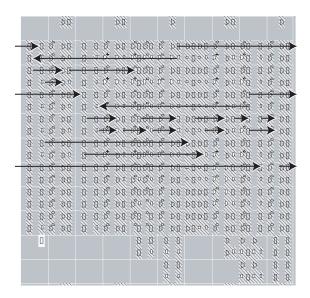

| 4.3               | A corner-turn FPGA interconnect. The C-boxes are implemented as full crossbars, while the S-boxes use capacity-depopulated crossbars to create corner turns, marked as T-boxes on this illustration.                                                                                                                                             | 36             |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

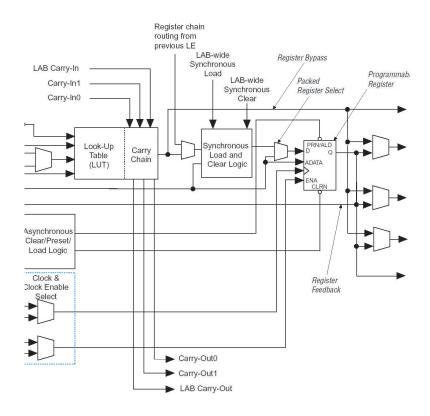

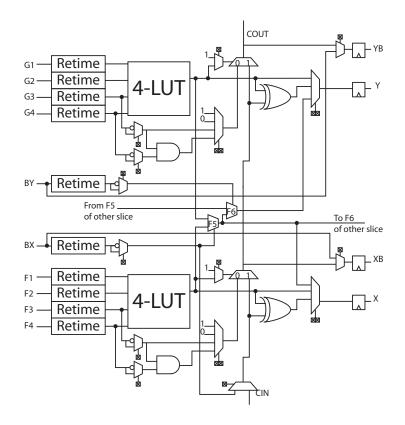

| 5.1<br>5.2<br>5.3 | The Slice used by the SFRA                                                                                                                                                                                                                                                                                                                       | 40<br>41<br>42 |

| 6.1               | (A) The conceptual structure of input retiming registers. Each input has a pro-<br>grammable shift register on the input. (B) The typical implementation of such shift-<br>registers. Only a single 2-1 mux delay is added to the critical path driven by the<br>retiming chain.                                                                 | 46             |

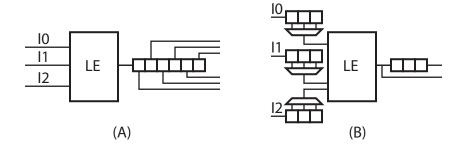

| 6.2               | The conceptual structure of (A) output retiming registers, and (B) Mixed retiming                                                                                                                                                                                                                                                                |                |

| 6.3               | registers                                                                                                                                                                                                                                                                                                                                        | 47<br>48       |

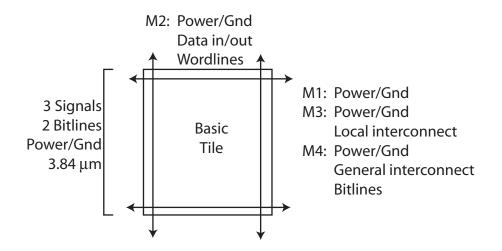

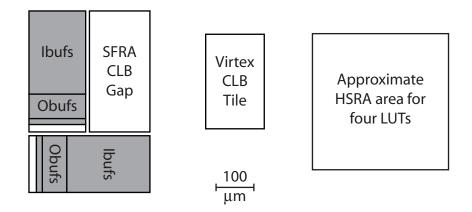

| 7.1               | The basic layer assignments. The tiles all are designed to tile along the top and bottom, so the power and ground connections are all routed along the tile boundries. Likewise, the overall tiles are designed to tile on the left and right sides as well. To create the vertical channel, the tiles are rotated 90 degrees. Metal 5 and 6 are | 53             |

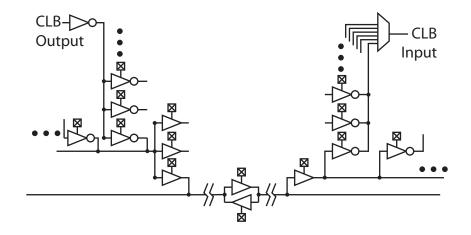

| 7.2               | reserved for routing independant signals over the tiles                                                                                                                                                                                                                                                                                          |                |

| 7.3               | broken and rebuffered every 3 CLBs                                                                                                                                                                                                                                                                                                               | 54             |

| 7.4               | mirrored copies                                                                                                                                                                                                                                                                                                                                  | 56<br>57       |

х

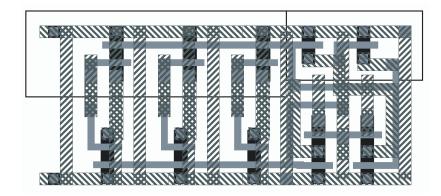

| 7.5  | The input buffer's tristate layout. Only the active, poly, N-wells, metal 1, and metal 2 layers are shown. The left side contains three tristates. The inputs arrive horizon-tally in metal 3 (not shown) and the outputs are processed vertically in metal 2. The other metal 2 connections are from the other group of tristates for the same input.                                                                      | 58       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

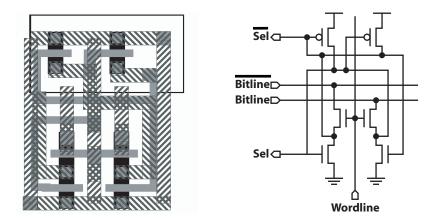

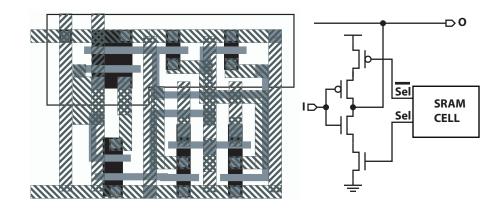

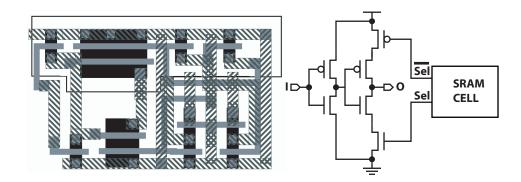

| 7.6  | The interconnect buffer layout with associated SRAM cell, and the corresponding circuit implemented. Only the active, poly, N-wells, metal 1, and metal 2 layers are shown. Both input and output occur on either metal 3 or metal 4, with the input                                                                                                                                                                        |          |

| 7.7  | driving the small inverter used to drives the large tristate                                                                                                                                                                                                                                                                                                                                                                | 59<br>60 |

| 8.1  | The two options considered by fanout routing, (A): starting horizontally and branch-                                                                                                                                                                                                                                                                                                                                        |          |

| 8.2  | ing vertically and (B), starting vertically and branching horizontally (A): The two possible single-turn routes. (B): An initial configuration before pushrout-<br>ing the connection between the gray boxes. (C): The configuration after pushrout-                                                                                                                                                                        | 65       |

| 8.3  | <ul><li>ing. In this example, each switchpoint supports only a single turn.</li><li>(A) The possible zig-zag routes which start horizontally and (B) The possible zig-zag routes which start vertically.</li></ul>                                                                                                                                                                                                          | 66<br>68 |

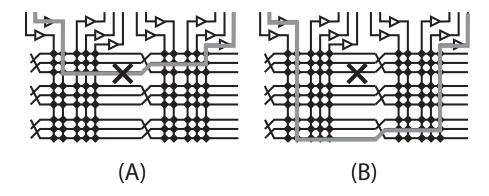

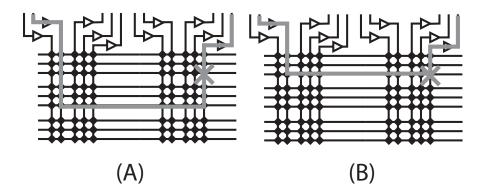

| 9.1  | (A) The gray signal is affected by the interconnect break marked with an X. (B) The                                                                                                                                                                                                                                                                                                                                         |          |

| 9.2  | <ul><li>gray signal is now rerouted to avoid the break.</li><li>(A) The gray signal is affected by the stuck-on interconnect point marked with an X. (B) The gray signal is now rerouted to use the stuck-on point.</li></ul>                                                                                                                                                                                               | 77<br>77 |

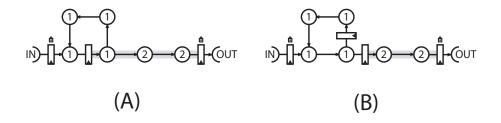

| 10.1 | (A): A small graph before retiming. The nodes represent logic delays, with the inputs and outputs passing through mandatory, fixed registers. The critical path is 5. The input and output registers can not be moved. (B): The same graph after retiming. The critical path is reduced from 5 to 4. Yet the I/O semantics have not changed, as it still requires three cycles for a datum to proceed from input to output. | 85       |

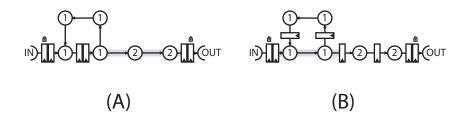

| 10.2 | (A): The example from Figure 10.1 which is converted to 2-slow operation. The critical path remains unchanged, but now the design will operate on two independant streams in a round-robin fashion. (B): The design is now retimed. By taking advantage of the extra flip-flops, the critical path has been reduced from 5 to 2                                                                                             | 89       |

| 11 1 |                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

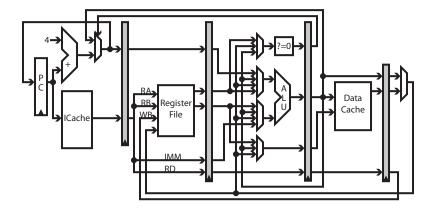

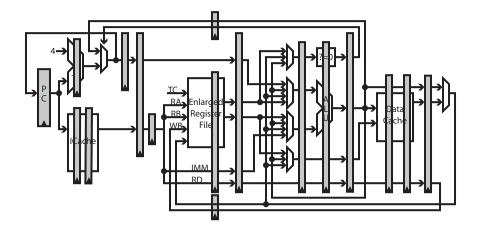

|      | A classic 5 stage microprocessor pipeline                                                                                                                                                                                                                                                                                                                                                                                   | 97<br>97 |

| 13.1 | The complete toolflow created for this research. This section focuses on the Xilinx                                                                                                                                                                                                                                                                                                                                         |          |

| 13.1 | -                                                                                                                                                                                                                                                                                                                                                                                                                           | 112      |

xi

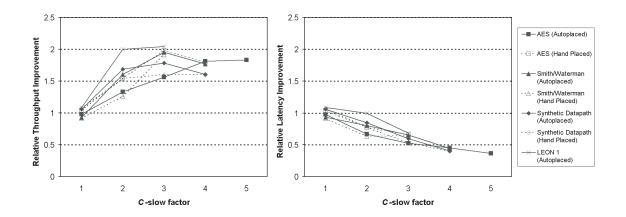

| 13.2 | C-slowing and retiming all the benchmarks and the effects on throughput and latency. A $C$ -slow factor of 1 just performs retiming. Throughput is substantially improved, roughly doubling the throughput in the best case. As expected, $C$ -slowing does increase the latency for a single computation. | 115 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

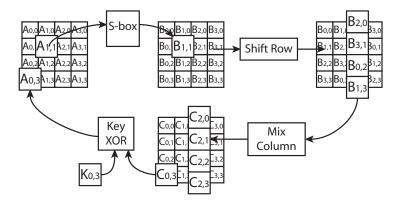

| A.1  | The AES round structure                                                                                                                                                                                                                                                                                    | 162 |

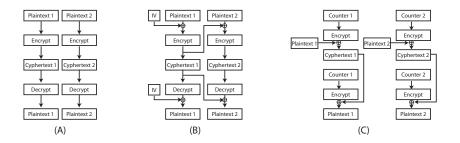

| A.2  | Three Common Operating Modes. A) Electronic Code Book (ECB), B) Cipher                                                                                                                                                                                                                                     |     |

|      | Block Chaining (CBC), C) Counter (CTR)                                                                                                                                                                                                                                                                     | 163 |

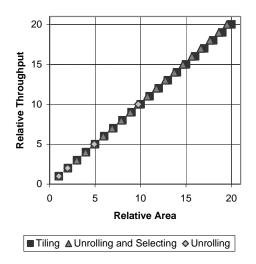

| A.3  | The relative area performance and throughput for tiling verses tiling different levels of unrolling verses just unrolling, for a cipher consisting of 10 repeated rounds,                                                                                                                                  |     |

|      | based on a 2.5% area savings for muxes and control logic when unrolling                                                                                                                                                                                                                                    | 165 |

| A.4  | The Subkey Generation Implementation in a Xilinx Spartan II-100. Arrowheads are                                                                                                                                                                                                                            |     |

|      | the location of pipeline stages, dataflow shown at 16 bit granularity.                                                                                                                                                                                                                                     | 167 |

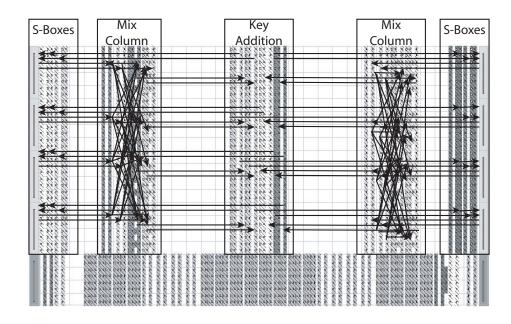

| A.5  | The Encryption Core Implementation in a Xilinx Spartan II-100. Arrowheads are                                                                                                                                                                                                                              |     |

|      | the location of pipeline stages, dataflow shown at 8 bit granularity                                                                                                                                                                                                                                       | 169 |

|      |                                                                                                                                                                                                                                                                                                            |     |

# **List of Tables**

| 4.1  | Comparing the costs of a full crossbar, $k$ physically-depopulated crossbar, and a $t$                                                                                                                                                                                    |     |