# INTERNATIONAL COMPUTER SCIENCE INSTITUTE

1947 Center Street • Suite 600 • Berkeley, California 94704 • 1-510-642-4274 • FAX 1-510-643-7684

# A Performance Analysis of the CNS-1\* on Large, Dense Backpropagation Networks

#### Connectionist Network Supercomputer

Silvia M. Müller smueller@icsi.berkeley.edu TR-93-046 September 1993

#### Abstract

We determine in this study the sustained performance of the CNS-1 during training and evaluation of large multilayered feedforward neural networks. Using a sophisticated coding, the 128-node machine would achieve up to 111 Giga connections per second (GCPS) and 22 Giga connection updates per second (GCUPS). During recall the machine would archieve 87% of the peak multiply-accumulate performance. The training of large nets is less efficient than the recall but only by a factor of 1.5 to 2.

The benchmark is parallelized and the machine code is optimized before analyzing the performance. Starting from an optimal parallel algorithm, CNS specific optimizations still reduce the run time by a factor of 4 for recall and by a factor of 3 for training. Our analysis also yields some strategies for code optimization.

The CNS-1 is still in design, and therefore we have to model the run time behavior of the memory system and the interconnection network. This gives us the option of changing some parameters of the CNS-1 system in order to analyze their performance impact.

<sup>\*</sup>The CNS-1 project is a collaboration of the University of California at Berkeley and the International Computer Science Institute

# Contents

| 1 |     | roduction 1                                  |

|---|-----|----------------------------------------------|

|   | 1.1 | Motivation                                   |

|   | 1.2 | Structure of the analysis                    |

| 2 | Mo  | delling the Timing                           |

|   | 2.1 | Memory system                                |

|   |     | 2.1.1 Memory hierarchy                       |

|   |     | 2.1.2 On-chip caches                         |

|   |     | 2.1.3 Main memory                            |

|   |     | 2.1.4 Refresh                                |

|   | 2.2 | Data network                                 |

|   |     | 2.2.1 Single transfer                        |

|   |     | 2.2.2 Multicast                              |

|   |     | 2.2.3 Multiple transfers                     |

|   | 2.3 | Datapath                                     |

|   |     | 2.3.1 Location of scalars                    |

|   |     | 2.3.2 Multiply-accumulate instructions       |

| 3 | Ber | schmark Problem 8                            |

|   | 3.1 | Description of the applications              |

|   |     | 3.1.1 Recall                                 |

|   |     | 3.1.2 Training                               |

|   | 3.2 | Parallelization and data distribution        |

|   |     | 3.2.1 Current approach                       |

|   |     | 3.2.2 Alternative approach                   |

| 4 | Per | formance Analysis of Kernel 1                |

| _ | 4.1 | Step 1: Reading the activations              |

|   |     | 4.1.1 I/O on the 128-node machine            |

|   |     | 4.1.2 I/O on the 1024-node machine           |

|   | 4.2 | Steps 2 and 3: Computation of the next layer |

|   |     | 4.2.1 Matrix vector multiplication           |

|   |     | 4.2.2 Global sum                             |

|   |     | 4.2.3 Sigmoid computation                    |

|   |     | 4.2.4 Interleaving the three main routines   |

|   |     | 4.2.5   | Penalty of I-cache misses                         | 21 |

|---|-----|---------|---------------------------------------------------|----|

|   | 4.3 | Step 4  | : Writing the results                             | 22 |

|   |     | 4.3.1   | Timing in the Torrent network                     | 23 |

|   |     | 4.3.2   |                                                   | 23 |

|   | 4.4 | Proble  | ems with the D-cache size                         | 23 |

|   |     | 4.4.1   | Steps 1 and 4                                     | 24 |

|   |     | 4.4.2   | Steps 2 and 3                                     | 24 |

| 5 | Per | formai  | nce Results of Kernel 1                           | 28 |

|   | 5.1 | Perfor  | mance results                                     | 28 |

|   |     | 5.1.1   | Detailed results under fixed conditions           | 28 |

|   |     | 5.1.2   | General results                                   | 29 |

|   |     | 5.1.3   | Implications for the CNS design                   | 30 |

|   | 5.2 | Influer | nce of the mapping and the parallelization scheme | 31 |

|   |     | 5.2.1   | Local optimizations                               | 32 |

|   |     | 5.2.2   | Global optimizations                              | 33 |

| 6 | Per | formai  | nce Analysis of Kernel 2                          | 34 |

|   | 6.1 | The fo  | prward pass                                       | 34 |

|   |     | 6.1.1   | I/O during training                               | 35 |

|   |     | 6.1.2   |                                                   | 35 |

|   | 6.2 | The b   |                                                   | 37 |

|   |     | 6.2.1   |                                                   | 37 |

|   |     | 6.2.2   |                                                   | 40 |

|   |     | 6.2.3   |                                                   | 44 |

|   | 6.3 | Cache   | 5 -                                               | 47 |

|   |     | 6.3.1   |                                                   | 47 |

|   |     | 6.3.2   |                                                   | 47 |

|   |     | 6.3.3   | -                                                 | 48 |

|   |     | 6.3.4   | -                                                 | 48 |

|   |     | 6.3.5   | <del>-</del>                                      | 49 |

| 7 | Per | formai  | nce Results of Kernel 2                           | 51 |

|   | 7.1 | Perfor  | mance results                                     | 51 |

|   |     | 7.1.1   | General results                                   | 51 |

|   |     | 7.1.2   | Detailed results under model conditions           | 52 |

|   | 7.2 | Influer | nce of the CNS specific optimizations             | 55 |

|   |     | 7.2.1   | Description of the optimizations                  | 55 |

|   |     | 7.2.2   | Performance impact of the optimizations           | 56 |

|   | 7.3 | Comp    |                                                   | 57 |

|   |     | 7.3.1   | <u>e</u>                                          | 57 |

|   |     | 7.3.2   | -                                                 | 58 |

|   |     | 7.3.3   |                                                   | 58 |

| 8            | Con | clusion                        | 59 |

|--------------|-----|--------------------------------|----|

|              | 8.1 | General results                | 59 |

|              | 8.2 | Implication for the CNS design | 59 |

|              |     | Optimization strategies        |    |

| $\mathbf{A}$ | Ass | embler Code                    | 61 |

|              | A.1 | Kernel 1: Recall               | 61 |

|              | A.2 | Kernel 2: Training             | 65 |

|              |     | A.2.1 Forward pass             | 65 |

|              |     | A.2.2 Backward pass            | 68 |

# Chapter 1

# Introduction

#### 1.1 Motivation

In the architecture specification of the CNS-1, Asanović et al sketch a benchmark application for this multicomputer and demand a performance of  $10^{11}$  connections per second:

"Extensive work in the area of connectionist speech understanding points to the need for a machine two to three orders of magnitude faster than the best machines available today. In condensed form, a statement of the requirements for the one abstract problem, representative of potential applications is: Evaluate the activations in a network with one million units having an average of a thousand connections per unit for a total of a billion connections. This should be done one hundred times per second." ([ABC+93], p. 5)

The question arises whether the CNS-1 can really execute such a benchmark with the required performance or not. As one result of the report, we will show that this is possible.

Since the CNS-1 is still in design, performance results have now the biggest impact for the following two reasons: First, detailed performance analysis can localize design bottlenecks, which at this stage it is fairly cheap to work out. Second, there are still some open aspects in the design. Our analysis should help the design team solving these problems.

This report is also motivated by the fact that programming the CNS-1 efficiently is not a trivial task. That is because the CNS-1 is a special purpose multicomputer with three levels of parallelism: the Torrent nodes work in a MIMD manner, each Torrent can execute up to four instructions at a time, and three of these instructions are vector operations. At the moment, there exists no efficient compiler for the machine, and therefore most of the code has to be hand optimized.

# 1.2 Structure of the analysis

The design team describes the design and the functionality of the CNS-1 very detailed in the technical reports [ABC<sup>+</sup>93, Asa93, AC93], but until now they have only sketched out the timing behavior of the memory system and the interconnection network. Since for our analysis we also need detailed information on these two components, we model them in

chapter 2. We try to keep the model as consitent as possible, but the design will definitely change over the next time, partially caused by the result of this report.

Chapter 3 deals with the benchmark, its specification and data distribution. Originally the recall of large nets was considered to be the only part of the benchmark application. We use the training as a second benchmark kernel. In the following four chapters we parallelize the two kernels, optimize their machine code, determine the run times and analyze the resulting performance. The last chapter summarizes the results and their possible impact on the machine design. We also sketch some strategies for CNS specific code optimization.

#### General Notation

In this document, **B** designates bytes, and **b** designates bits.

#### Acknowledgments

This work has benefitted a lot from discussions with various members of the realization and CNS groups at ICSI. I would particularly like to thank Krste Asanović, Jim Beck, Tim Callahan, Jerry Feldman, David Johnson, Brian Kingsbury, Phil Kohn, Nelson Morgan and John Wawrzynek.

# Chapter 2

# Modelling the Timing

The Connectionist Network Supercomputer (CNS-1) has been designed for neurocomputation and should reach high performance even on sparsely connected neural networks; this at least is one goal of the project [ABC+93]. The CNS is a multicomputer with distributed memory, based on a super-scalar design. The nodes are connected via a mesh with wraparound in one dimension. Each processor has a scalar unit and three coprocessors: a network interface, a memory unit, and a small SIMD array. The scalar unit is a MIPS-based design extended by a few instructions to communicate with its coprocessors. The SIMD unit is accessed via vector operations. The details of the hardware and the ISA are described in [ABC+93, Asa93, AC93].

#### 2.1 Memory system

#### 2.1.1 Memory hierarchy

The CNS-1 has a three level memory hierarchy: separate instruction and data cache on the processor chip, a second level cache in each RDRAM chip, and the RDRAM itself. All the caches are direct mapped, and their capacity is given in Table 2.1.

|             | Cache Size | Line Size               | No. of Lines |

|-------------|------------|-------------------------|--------------|

| I-Cache     | 4KB        | $(32 \times 4B) \ 128B$ | 32           |

| D-Cache     | 4KB        | 32B                     | 128          |

| RDRAM-Cache |            |                         |              |

| 4.5 Mb chip | 2KB        | 1KB                     | 2            |

| 18 Mb chip  | 4KB        | 2KB                     | 2            |

Table 2.1: Cache capacity

|        |         | Read     |          | Write   |          |          |

|--------|---------|----------|----------|---------|----------|----------|

| RDRAM  | Hit     | Miss     |          | Hit     | Miss     |          |

|        | 1116    | /dirty   | dirty    | 1116    | /dirty   | dirty    |

| 4.5 Mb | 48 + 2x | 152 + 2x | 152 + 2x | 16 + 2x | 120 + 2x | 120 + 2x |

| 18 Mb  | 44 + 2x | 112 + 2x | 156 + 2x | 12 + 2x | 64 + 2x  | 108 + 2x |

Table 2.2: Main memory access time for x Byte [ns]

#### 2.1.2 On-chip caches

The I-cache delivers one instruction per CPU cycle; a cache miss takes between 20 and 45 cycles. This time includes the memory access and the update of the I-cache. In this analysis we always assume the worst case for the delay of an I-cache miss.

The D-cache supports byte, half word and word mode. Both, scalar and vector unit, can access the D-cache, but only one at a time. A scalar access takes one cycle; a vector access needs [vlength/32] cycles to be completed. In the case of a cache miss, the delay of the main memory has to be added to the access times.

The D-cache is not large enough to store all the data. Less frequently used data should only be stored in the main memory. We assume that there are special load and store instructions to access these data, so that they can bypass the cache, and that the CPU still can access the D-cache during the RDRAM ports are executing some requests.

#### 2.1.3 Main memory

The memory consists of four banks, each connected to its own memory interface. Each interface controls four RDRAM chips. The ports are interleaved every 32B and the banks every 128B. Therefore, neighboring 32B blocks are always addressed via different ports. Every fourth block is stored in the same port but only every sixteenth block is stored in the same memory chip. The four ports work in parallel.

The memory access time mainly depends on three parameters: the capacity of the RDRAM chip, the type of the access (read/write), and whether the data are in the RDRAM cache or not. In the case of a cache miss, the access time also depends on the dirty flag; the write back of a dirty cache line takes some additional cycles (Table 2.2). The data sheets [Ram92, Tos92b, Tos92a] specify the memory access times in nanoseconds, but all our analysis is done in cycles. We assume that one CPU cycle of the CNS takes 8 ns.

#### 2.1.4 Refresh

The refresh of the RDRAMs has to be started at least every 1024  $\mu$ s (128000 cycles) and takes about 1  $\mu$ s (125 cycles). In the best case all refreshes occur when the main memory is idle and so they do not affect the run time of the benchmark. However, it is much more likely that some refreshes will contend with memory accesses and therefore delay the execution of the kernels. In the worst case the run time increases by a factor of  $\tau_{ref} = 1024/(1024 - 1)$ , that is less than 0.098 %.

#### 2.2 Data network

There are only three types of transfers in our benchmark: single transfer, multicast and multiple transfers.

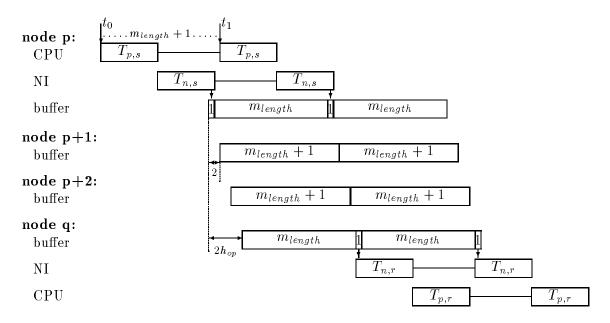

The processor overhead for sending and receiving messages is fairly small, because of active messages [CSS+91]. In our analysis, we assume that they are  $T_{p,s} = T_{p,r} = 10cc$  (CPU cycles). This includes the overhead of moving the data to the transfer registers. We also assume that the overhead in the network interface for sending and receiving is of the same magnitude:  $T_{n,s} = T_{n,r} = 10cc$ . The message length  $m_{length}$  is counted in bytes; it is the amount of data plus nine header bytes. ([Cal93, AC93] gives a detailed description of the network interface.)

#### 2.2.1 Single transfer

Under a single transfer we understand, that a processor p sends a message to a processor q, and that there is no further activity going on which could block the transfer. The message has to performe  $h_{op}$  network hops. Figure 2.1 illustrates the timing of such a transfer; the message is 20 bytes long and passes two intermediate nodes, p + 1 and p + 2. In general, a single transfer works as follows:

- Node p switches to the handler and prepares the message. This takes  $T_{p,s}$  units of time. After that p is free for other work and the network deals with the message.

- After time  $T_{p,s}$  the network interface of node p deals with the message.  $T_{n,s}-1$  cycles later the global part of the interface gives the message to the direction-dependant part of the hardware which is then busy for  $m_{length}$  cycles.

- A package leaves the buffer one cycle after it arrived, and spends one cycle in the link. Each hop in the network therefore delays the message by two cycles.

- The interface of node q receives the first byte after  $T_{p,s} + T_{n,s} + 2h_{op}$  cycles and has to deal with this message for  $m_{length} 1 + T_{n,r}$  cycles.

- Now processor q gets an interrupt and switches to the handler. Reading the message out of its network interface takes additional  $T_{p,r}$  cycles.

In the best case the whole transfer takes time

$$T_{ST}(h_{op}) = T_{p,s} + T_{n,s} + 2h_{op} - 1 + m_{length} + T_{n,r} + T_{p,r}.$$

Node p can send the next message to node q without any network conflicts  $m_{length} + 1$  cycles after it started the previous transfer. The network buffers are the critical hardware elements. They deal  $m_{length} + 1$  cycles with a transfer. After that time, they are able to receive a new package from the same direction.

Under real circumstances, it is possible that an interrupt can not be executed immediately or that a package is blocked for a while. This delay increases the transfer time  $T_{ST}$ .

Figure 2.1: Timing diagram for sending a 20B message from p to q via nodes p+1 and p+2.

#### 2.2.2 Multicast

The CNS-1 has a simple but quite effective mechanism that allows a multicast to be executed as fast as a single one-to-one transfer. A special flag in the message header gives the option to a sender to drop off a copy of the message at every node along the path from the source to the destination.

When receiving a message with an active multicast flag, the router forwards it to a network link and to the CPU. The router is a crossbar, and therefore routing the message to one or two buffers requires the same amount of time.

This is not a mechanism for general multicast or broadcast, but it is sufficient for distributing data along columns or rows of the processor network. It is the fastest mechanism for that type of multicast.

#### 2.2.3 Multiple transfers

This type of transfer involves 2k adjacent nodes  $(1 \le k \le 16)$ . The first k nodes  $p_1, \dots, p_k$  send messages to the remaining k nodes and vice versa.

transfer 1:  $p_i$  sends to  $p_{i+k}$   $1 \le i \le k$ transfer 2:  $p_{i+k}$  sends to  $p_i$

Both transfers occur at the same time and will not interfere with one another because they use different parts of the network. For a ring of 32 nodes it is a bit different. The direction of the message alternates from node to node, but this makes the transfer only faster. The transfer from node  $p_k$  to  $p_{2k}$  takes  $T_{ST}(k) = 40 + 2k - 1 + m_{length}$  cycles. The other k-1 messages have to use the same part of the network, therefore they are blocked for a while. The message of node  $p_{k-i}$  is delayed for  $i \cdot m_{length}$  cycles. Without further problems the whole transfers complete in  $T_{MT}(k) = T_{ST}(k) + (k-1) \cdot m_{length} = 39 + 2k + k \cdot m_{length}$  cycles.

#### 2.3 Datapath

We make two assumptions for the datapath which might not be consistent with the CNS-1 design. One is the location of the scalars for vector operations, and the other is the execution of a multiply-accumulate instruction. At the moment the implementation of these aspects is still open. We will therfore analyze the performance impact of different solutions but in general we assume the following:

#### 2.3.1 Location of scalars

Some vector operations require scalars. These variables can only be changed by the scalar unit, but the vector unit can read them. We assume that they are stored in a special register file in the vector unit. The scalar unit reads and writes this register file via special move instructions.

It is also possible, to store them in the register file of the scalar unit. This solution requires less hardware, but makes the register file control more complicate.

#### 2.3.2 Multiply-accumulate instructions

We assume that the arithmetic vector unit VP0 has a special multiply-accumulate instruction, and that this instruction takes as long as a multiply instruction. This is possible in the current design of the CNS-1 datapaph but it requires a change in the machine language and the control logic.

# Chapter 3

# Benchmark Problem

Detailed performance analyses require a specification of the workload. In the field of neurocomputing the workload is usually defined as the recall step of a connectionist network. On the other hand, the CNS-1 should be used for studying large connectionist networks and designing new neuroalgorithms. This implies that a huge amount of computing time will be spent training the networks. For these reasons, both training and recall should be represented in the benchmark.

#### 3.1 Description of the applications

Our benchmark focuses on dense three-layer networks with about  $10^9$  connections. The first kernel deals with recall and the second with training. We use a backpropagation algorithm described in [MR88, Gre92]. The underlying neural network has one hidden layer which is completely connected to the other two layers. The network has  $n_i$  inputs,  $n_h$  hidden nodes, and  $n_o$  outputs, and its size varies between 201.3 million and 1.34 billion connections. The input patterns are mapped into several classes with 64 subclasses each. The size of the layers is listed in Table 3.1.

When presenting a pattern to the input layer, the information stored in the weight matrices and bias vectors are used to compute an output vector. We call this step recall.

|             | Global Size |       |       |                   | Local Size |          |          | Machine Size |       |         |

|-------------|-------------|-------|-------|-------------------|------------|----------|----------|--------------|-------|---------|

| Connections | $n_i$       | $n_h$ | $n_o$ |                   | $n_{pi}$   | $n_{ph}$ | $n_{po}$ | $p_i$        | $p_h$ | # Nodes |

| 192M        | 8K          | 16K   | 4K    | $(64 \times 64)$  | 1024       | 1024     | 512      | 8            | 16    | 128     |

| 768M        | 16K         | 32K   | 8K    | $(128 \times 64)$ | 2048       | 2048     | 1024     | 8            | 16    | 128     |

| 1536M       | 16K         | 64K   | 8K    | $(128 \times 64)$ | 2048       | 4096     | 1024     | 8            | 16    | 128     |

| 768M        | 16K         | 32K   | 8K    | $(128 \times 64)$ | 1024       | 512      | 512      | 16           | 64    | 1024    |

| 1536M       | 16K         | 64K   | 8K    | $(128 \times 64)$ | 1024       | 1024     | 512      | 16           | 64    | 1024    |

Table 3.1: Size of the neural network and dimension of the local connection matrices, when parallelized as defined in section 3.2.1

When presenting an input and a result pattern at the same time, both vectors are used to update the information stored in the neural network. This step is called *training*.

#### 3.1.1 Recall

During recall, the machine reads an activation vector. This input vector **i** specifies the values of the input layer of the neural network. The values of the hidden vector **h** are then obtained combining the input vector with the weight matrix **A** and the bias vector **a**. **A** and **a** are related to the first two network layers. In the following step the values of the output vector **o** are computed by combining the hidden vector with the weight matrix **B** and the bias vector **b**, both related to the second and third layer. Mathematically the recall or *forward pass* for one pattern can be described as follows:

read(i)

$$\mathbf{h} = \mathbf{A} \cdot \mathbf{i} + \mathbf{a}$$

$\forall x : \mathbf{h}[x] = 1/(1 + \exp(\mathbf{h}[x]))$

$\mathbf{o} = \mathbf{B} \cdot \mathbf{h} + \mathbf{b}$

$\forall x : \mathbf{o}[x] = 1/(1 + \exp(\mathbf{o}[x]))$

write( $\mathbf{o}$ )

In the following text, we refer to step 3 (5) of this code as the sigmoid computation of vector  $\mathbf{h}$  (o). The sigmoid computation is often implemented as table lookup. In our implentation, the elements of the input, hidden and output vector are one byte wide, the elements of the weight matrices and bias vectors are two bytes wide, and intermediate results like partial sums are 4 bytes wide.

#### 3.1.2 Training

During training the machine also computes an output vector for each input vector, but in a second phase it compares the output with the required result  $(\mathbf{r})$ , computes the error vectors of the output and hidden layers  $(\mathbf{eo}, \mathbf{eh})$ , and updates the weight matrices and bias vectors. For one pattern, the formal description of the training step is given below; fac is the learning rate and  $\langle x, y^T \rangle$  the outer product of the vectors x and y.

```

Forward pass:

Error backpropagation:

eh = B^T \cdot eo

read(\mathbf{i}, \mathbf{r})

\forall x : \mathbf{eh}[x] = \mathbf{h}[x](1 - \mathbf{h}[x]) \, \mathbf{eh}[x]

\mathbf{h} = \mathbf{A} \cdot \mathbf{i} + \mathbf{a}

\forall x : \mathbf{h}[x] = 1/(1 + \exp(\mathbf{h}[x]))

o = B \cdot h + b

Weight update:

\mathbf{B} = \mathbf{B} - fac \cdot < \mathbf{eo}, \mathbf{h^T} >

\forall x : \mathbf{o}[x] = 1/(1 + \exp(\mathbf{o}[x]))

\mathbf{b} = \mathbf{b} - fac \cdot \mathbf{eo}

A = A - fac \cdot \langle eh, i^T \rangle

Error in the output layer:

\mathbf{a} = \mathbf{a} - fac \cdot \mathbf{eh}

eo = r - o

```

In this report, we refer to the training step without the forward pass as the *backward pass*. In our implementation, the elements of the error vectors are two bytes wide, the width of the other data is as described before.

#### 3.2 Parallelization and data distribution

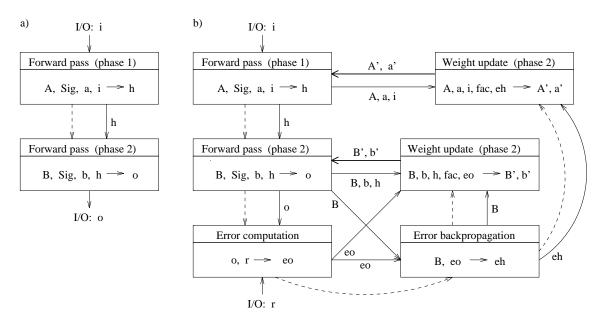

Both kernels mainly consist of matrix-vector operations, and it is well known how to parallelize these. Additional parallelism could come from the fact that these algorithms have to be executed for a huge number of patterns. The data and control flow graphs in figure 3.1 can show whether it is possible to pass several patterns at a time through the network.

Figure 3.1: Data flow and high level control flow of recall (a) and training (b). Sig stands for the sigmoid lookup table. Dashed arrows indicate the control flow, solid arrows indicate the data flow. The weight updates change the matrices of the next iteration, these dependencies are indicated by fat arrows.

**Recall** There are only a few data dependencies in the recall code, all of them are based on input or result vectors. The flow graphs are acyclic and several patterns can therefore be executed in parallel. This makes recall a highly parallel problem and gives us mainly three options for parallelization:

- Both weight matrices are spread over the whole multicomputer but the processors execute each procedure for several patterns at a time.

- The multicomputer is divided into two groups of processors. One group executes phase 1 in parallel the other group executes phase 2. The execution of both phases is pipelined.

- The processing nodes are divided in several groups. The neural network is duplicated, and one copy is assigned to each group of processors. The groups work in parallel but on different input patterns.

The third version stores several copies of the network data, and therefore needs much more storage space then the other two versions. That would definitely be a problem, especially for large neural networks. In the following, we will therefore only consider the first two options.

Training The weight updates change the information stored in the neural network, that causes cycles in the data flow graph. One cycle even includes the first and the last procedure of the training code. Consequently, the processors first have to finish one pass through the network before they can start the next pass. Training therefore has less parallelism than recall. The parallelism comes from the matrix vector operations or from the branches in the control flow.

#### 3.2.1 Current approach

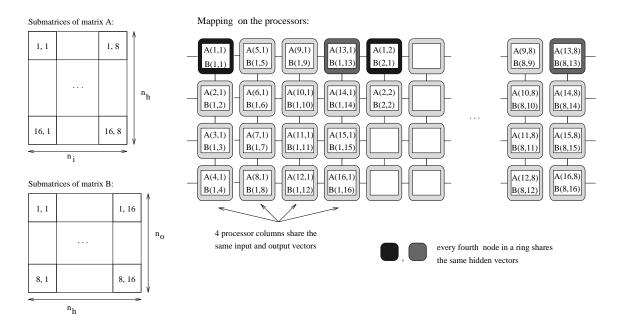

The bias vectors are mapped into the last column of the connection matrices. For performance reasons we store the extended matrices in column-major order. They are distributed blockwise over all processors. The local matrices have the dimensions  $n_{pi} \times n_{ph}$  and  $n_{ph} \times n_{po}$ , with  $n_{pi} = n_i/p_i$ ,  $n_{ph} = n_h/p_h$  and  $n_{po} = n_o/p_h$ ;  $p_h \ge p_i$ . Besides these matrices, the nodes also store the corresponding parts of the inputs, hidden units and outputs;  $p_i$  processors share the same inputs and outputs, and  $p_h$  processors deal with the same hidden units. Nodes sharing the same hidden units are located in a ring of the processor network. Nodes sharing inputs are arranged in neighbored columns. Figure 3.2 illustrates the distribution for the 128-node machine.

The dimensions of the local matrices are chosen so that most of the activations and results can be stored in the on-chip caches. This implies that  $n_{pi}$  and  $n_{ph}$  nearly have the same size. We also make the restriction that  $n_{pi}$  is a multiple of four, and the other two dimensions are multiples of 64. For our analysis we assume that the dimensions of the matrices are powers of two.

This distribution can be used for recall and training, makes a good use of the on-chip data cache, and keeps the amount of transfer fairly small. There occur  $p_h$  global sums when computing a hidden vector. The global sums involve  $p_i$  nodes each, and can be executed in parallel.  $p_i$  global sums have to be executed in parallel when computing a vector of the input or output layer. There are  $p_h$  nodes involved in each of them. This transfer can widely be overlapped with computation, because of active messages.

Kumar et al. analyzed in [KSA93] several parallel formulations of the backpropagation algorithm for multilayered feedforward networks. They showed that the blockdistribution we are using is optimal for hypercubes and related architectures when using per-pattern training. We still have to addapt their formulation, because the CNS-1 has a barrel topology, uses active messages and has a powerful vector unit.

#### 3.2.2 Alternative approach

During recall, it is possible to compute the hidden and output vectors in a pipelined manner. One part of the machine deals with the first three steps of recall, the other part only deals with the remaining three steps. The first group of processors reads the input vector,

Figure 3.2: Mapping the submatrices on the 128-node machine. Four neighbored columns share the same input and output vectors. In a fixed ring, every fourth node belongs to the same group. Nodes of such a group share the same hidden vectors.

broadcasts it to each node in the group, computes the hidden vector and send it to the next group of processors. The second group receives the hidden vector and broadcasts it to each node in the group, computes the output vector and writes the result to the outside world. After sending the hidden vector to the other group, the first processors can already deal with the next input pattern.

This data distribution also requires only a small amount of transfer, and most of that transfer will not be visible, because it can be overlapped with computation. But compared with the previous distribution, this version has two major drawbacks. That is the reason why we chose the first distribution.

First, this distribution can not efficiently be used in the training of networks. Half of the processors would be idle because of data dependencies. Training is much more timeconsuming than recall, and therefore a performance loss of 50% really hurts.

Second, each node has to see the whole input or hidden vector. These vectors are usually too large for the on-chip data cache, therefore they have to be accessed in the main memory. The main memory also handeling two matrix accesses already is a bottleneck. Additional memory requests therefore slow down the execution.

# Chapter 4

# Performance Analysis of Kernel 1

Kernel 1, the recall of a dense, three-layer neural network, has to be executed for several patterns; two of them are passed through the network at the same time. That makes it much easier to hide the latency of the main memory. The kernel works in four steps.

The I/O nodes get two activations from the outside world and distribute them over the whole machine. In the second step, the processing nodes compute the values of the hidden units. Third, the nodes combine these values with the second connection matrix and produce two result vectors. During the fourth step these vectors are stored in main memory, and the processors in the bottom row send the results to the I/O nodes. They transfer the data to the outside world. The second and the third step use the same procedures, but with different data.

Each of the four steps has two types of procedures, one with network activity and one with local computation or I/O. Procedures of different types can be interleaved. That makes it possible to hide the latency of the processor network.

The I/O nodes and the processing nodes run different programs. The following pseudocode (Table 4.1) shows the structure of both programs. Code optimization is considered later on. Variables starting with R or r refer to the abstract use of vector and scalar registers.

### 4.1 Step 1: Reading the activations

This step runs on several levels: outside world, I/O nodes, and processing nodes. The I/O nodes get the data from the outside world and distribute them over the processing nodes. The processors receive their part of the activations and store them in the data cache and the main memory.

We assume that the outside world communicates with the CNS only via one fourth of the I/O nodes; the data have to be transferred over 32/4 = 8 H-ports, each with a bandwidth of 64 bit per 20 ns (400MB/s).

One Hydrant has to read the activations for four columns of processing nodes. In the large machine (1024 nodes) all these Torrents share the same activations, but in the 128-node machine only two columns of processors use the same activations.

#### Hydrant program

#### Torrent program

```

for i=1, # patterns, 2

for i=1, # patterns, 2

\{ \text{ for } j=1, \text{ npi}, 128 \}

{ get-activ(Vi1, Vi2, npi)

read(Vi1[j:j+127])

layer(1, npi, nph, M1, Vi1, Vi2, Vh1, Vh2)

for j=1, npi, 128

layer(2, nph, npo, M2, Vh1, Vh2, Vo1, Vo2)

read(Vi2[j:j+127])

out-res(Vo1, Vo2, npo)

for j=1, npo, 128

}

read(Vo2[j:j+127])

for j=1, npi, 128

read(Vo2[j:j+127])

}

```

Table 4.1: Coarse structure of the first step

#### 4.1.1 I/O on the 128-node machine

The nodes  $H_a, \dots, H_d$  are four neighboring Hydrants.  $H_b$  and  $H_a$  broadcast the same vectors to the Torrents and so do  $H_c$  and  $H_d$ . An H-port is connected to  $H_b$  which has to read the data for both groups of processors. The different pseudocodes are shown in Table 4.2. The first argument in a send instruction codes how far the message has to go up a column and the second argument codes the number of hops in the ring.

The run time of this step mainly depends on three quantities: the overhead in the Hydrant network, the time for distributing 128 bytes to the Torrents, and the time between two of these broadcasts. Transfers are either single transfers or multicasts; both take  $T_{ST}(h_{op})$  cycles. All messages are 137 bytes long.

#### Timing in the Hydrant network

Node  $H_b$  reads two vectors of 128 bytes each via the H-port. That takes 6 cycles per vector. There also occurs some overhead based on protocols. Therefore we assume that the reading of 128 bytes takes 20 cycles; resulting in 40 cycles for reading two vectors. The CPU then starts the broadcast to the nodes  $H_c$  and  $H_d$ , and the transfer to node  $H_a$ . That takes  $2 \cdot T_{p,s} = 20$  cycles. Afterwards  $H_b$  broadcasts the vector of the previous iteration along the network column. That keeps the CPU busy for 10 cycles. In the next  $1 + l_{oop}$  cycles the CPU saves the current vector in a vector register and executes the loop overhead.

Two transfers with the same sender and receiver must be separated by  $m_{length} + 1$  cycles. That implies that one pass of the loop takes

$$max(40 + 3T_{s,p} + 1 + l_{oop}, m_{lenght} + 1) = max(71 + l_{oop}, 138) = 138$$

cycles. The first part of the  $H_b$  code is almost the same as the loop body, only the broadcast to the Torrents is missing. The node  $H_b$  therefore starts the first transfer to the Torrents after  $m_{length} + 1 + 40 + 2T_{s,p} = m_{length} + 61$  cycles.

Node  $H_a$  distributes the first 128 bytes after  $40 + T_{p,s} + T_{ST}(1) = 91 + m_{length}$  cycles,  $H_c$  after  $40 + T_{ST}(1) = 81 + m_{length}$  cycles, and  $H_d$  two cycles later than  $H_c$ . Therefore the

```

Code for Hydrant H_b

Code for Hydrant H_a, H_c, H_d

for i=1, 2*npi, 128

get-byte(128, Ri1[0:31]);

get-byte(128, Ri2[0:31]);

{ receive(128, Ri1[0:31]);

b cast(32, 0, Ri1[0:31]);

bcast(0, 2, Ri1[0:31]);

send(0, -1, Ri2[0:31]);

Ri3[0:31] = Ri2[0:31];

for j=129, 2*npi, 128

Code for Torrent

{ get-byte(128, Ri1[0:31]);

get-byte(128, Ri2[0:31]);

for j=1, npi, 128

bcast(0, 2, Ri1[0:31]);

{ receive(128, Ri1[0:31]);

send(0, -1, Ri2[0:31]);

Vi1[i:i+127] = Ri1[0:31].b;

bcast(32, 0, Ri3[0:31]);

Ri3[0:31] = Ri2[0:31];

for j=1, npi, 128

{ receive(128, Ri1[0:31]);

bcast(32, 0, Ri3[0:31]);

Vi2[i:i+127] = Ri1[0:31].b;

```

Table 4.2: Pseudocode for reading and distributing the activations

startup in the Hydrant network takes between  $61 + m_{length}$  and  $92 + m_{length}$  cycles. Further broadcasts to the Torrents can be started every 138 cycles. This time is also sufficient for reading new data and sending them to the other Hydrants.

#### Timing in the Torrent network

The Torrents in the top row of the machine receive the message  $T_{ST}(32) = 103 + m_{length} = 240$  cycles after the corresponding Hydrants started the transfer. New data arrive every  $m_{length} + 1 = 138$  cycles. The CPU needs ten cycles to receive the data from the network interface. The remaining 127 cycles can be used for storing the data in the cache and the main memory and executing loop overhead. The run time of these operations is visible only when storing the last vector. We can assume that the last write is a hit, so storing a vector in the cache and main memory takes 4 + 10 = 14 cycles.

In the worst case, code and data are not in the RDRAM cache, and the cache lines are dirty. Loading a block of 32 instructions takes 45 cycles. The data can be stored in  $(120+2\cdot128)/8=47$  cycles (4.5 Mb memory chip). Even with loop overhead that still fits into the 127-cycle slot without additional time penalty.

#### Penalty for I-cache misses

Node  $H_b$  has the longest program. The code of its main loop should still fit into two blocks.  $H_b$  also executes the code of three message handlers with at most 32 instructions each. The processor loads five blocks for the main procedure and three for the handlers. At worst, all these codes use the same space in the I-cache. Then the processor has to load four blocks

```

\begin{array}{lll} \text{get-byte}(128,\,\text{Ri1}[0:31]); & \text{bcast}(0,\,3,\,\text{Ri1}[0:31]); \\ \text{bcast}(0,\,3,\,\text{Ri1}[0:31]); & \text{bcast}(32,\,0,\,\text{Ri3}[0:31]); \\ \text{Ri3}[0:31] = \,\text{Ri1}[0:31]; & \text{Ri3}[0:31] = \,\text{Ri1}[0:31]; \\ \text{for } j{=}129,\,2^*\text{npi},\,128 & \} \\ \{\,\,\text{get-byte}(128,\,\text{Ri1}[0:31]); & \text{bcast}(32,\,0,\,\text{Ri3}[0:31]); \end{array}

```

Table 4.3: Pseudocode of kernel 1 for the Hydrants  $H_a$

per loop iteration. That makes  $2 + 5n_{pi}/64$  blocks. Each block prolongs the execution time by 44 cycles.

The following formulas show the kernel run time and the penalty caused by I-cache misses. Each node handles one procedure per pass of kernel 1; that requires  $T_{proc}$  cycles. RDRAM refreshes can increase the run times at most by a factor of  $\tau_{ref}$ .

$$\begin{array}{lcl} T_{step1} & = & H_{startup} + \frac{n_{pi}}{64} (m_{length} + 1) + 14 + 102 + T_{proc} \\ H_{startup} & \leq & 92 + m_{length} = 229 \\ P_{enalty} & \leq & 44 \left(2 + \frac{5n_{pi}}{64}\right). \end{array}$$

There are two ways to hide the startup time of the Hydrant network. First, the Hydrants know whether they have to deliver further patterns or not. Therefore they can read the next two patterns and distribute them in their local network during the computation steps 2 and 3. The broadcast to the Torrents is then triggered by the end of step 4. Second, the Hydrants also have D-caches. During step 2 they read as many data of the next two patterns as they can store in the cache.

#### 4.1.2 I/O on the 1024-node machine

On the large machine, four columns of Torrents share the same activations. That makes the I/O-step a bit simpler. The code for the Torrents and Hydrants with no H-port are the same; only the nodes with H-port execute different code, and the partitioning of the Hydrants has changed. Now  $H_a$  has the H-port; it reads the activations and distributes them to the three neighboring Hydrants  $H_b$ ,  $H_c$  and  $H_d$  via a multicast. Afterwards all four nodes broadcast the vector to the Torrents (Table 4.3).

These changes only influence the overhead in the Hydrant network. The network bandwidth still limits the time between two broadcasts to the Torrents to  $m_{length} + 1$  cycles. Node  $H_a$  delivers the first vector to the Torrents after  $m_{length} + 1 + 20 + T_{p,s} = m_{length} + 31$  cycles.  $H_b$  starts the broadcast after time  $20 + T_{ST}(1) = 61 + m_{length}$ ;  $H_c$  starts it two cycles later and  $H_d$  four cycles later. Now the startup varies between  $31 + m_{length}$  and  $65 + m_{length}$  cycles.

```

for i=0, np2 - 1, 64;

/* global sum */

{ /* matrix vector multiplication */

gsum(Rt1[0:63],st);

Rt1[0:63] = Rt2[0:63] = 0;

gsum(Rt2[0:63],st);

for j=0, np1 - 1, 4

/* sigmoid table lookup */

\{ \operatorname{rd1}[0:3] = \operatorname{Vi1}[j,j+3];

rd2[0:3] = Vi2[j,j+3];

Rt1[0:63] = clip(Rt1[0:63]);

for k=0, 3

Rt2[0:63] = clip(Rt2[0:63]);

\{ Rt1[0:63] += rd1[k] * M[j+k][i;i+63];

Vo1[0:63] = Sigm[Rt1[0:63]];

Vo2[0:63] = Sigm[Rt2[0:63]];

Rt2[0:63] += rd2[k] * M[j+k][i;i+63];

}

}

}

```

Table 4.4: Pseudocode for the forward routine of kernel 1

#### 4.2 Steps 2 and 3: Computation of the next layer

Steps 2 and 3 execute the same code but on different data. The code only runs on the processing nodes. Their pseudocode is shown in Table 4.4;  $n_{p1}$  and  $n_{p2}$  are the dimensions of the local activation and result vectors. The parameter st specifies whether the second or third layer should be computed; st only influences the code for global sum. For better performance, the assembler code uses some optimizations which are not shown in the pseudocode. The inner loop of the matrix vector multiplication is unrolled, and the outer loop is software pipelined. The execution of the three routines of this kernel – matrix vector multiplication, global sum and sigmoid computation – are interleaved.

The local data can be stored at different levels of the memory hierarchy; this influences the run time of the kernel. There are mainly three versions:

- D-cache stores all local activations and results of one layer,

- D-cache only stores the local activations.

- D-cache only stores parts of the local activations and results.

The first case is assumed to be the default, but that is not feasible for large local vectors and a limited cache size. In a separate section we analyze those cache problems.

At the end of step 1 the two local input vectors are stored in the on-chip cache. During step 2 the processors combine the inputs with the first weight matrix and produce values for the hidden units. They store these results in the cache. The results of the second step are the inputs of third. Therefore the inputs of step 3 are also in the D-cache when step 3 starts its execution.

#### 4.2.1 Matrix vector multiplication

The activation are one byte wide; and the CPU can load four activations from the D-cache with one word access. Later on the CPU extracts the data byte by byte. The weights are

|        | Hit               | M                  | Hit                | Mi       | SS         |           |

|--------|-------------------|--------------------|--------------------|----------|------------|-----------|

| RDRAM  | 1110              | /dirty             | dirty              | 1116     | /dirty     | dirty     |

|        | $r_h$             | $r_{m,/d}$         | $r_{m,d}$          | $r_h$    | $r_{m,/d}$ | $r_{m,d}$ |

| 4.5 Mb | $48 + 2 \cdot 32$ | $152 + 2 \cdot 32$ | $152 + 2 \cdot 32$ | 14       | 27         | 27        |

| 18 Mb  | $44 + 2 \cdot 32$ | $112 + 2 \cdot 32$ | $156 + 2 \cdot 32$ | 14       | 22         | 28        |

|        |                   | [ns]               |                    | [cycles] |            |           |

Table 4.5: Reading 32B via one Rambus port

directly loaded from the main memory, bypassing the D-cache. The processor accesses 32 elements with two bytes each. The data are 32B aligned, so two memory ports will execute the request in parallel. This access time depends on the actual status of the main memory and the size of the RDRAM chips (Table 4.5).

#### Cache analysis

There are 16 memory chips, each has two cache lines of size  $l_{RDC}$ . For small memory chips  $l_{RDC}$  is 1KB, and 2KB for large chips (Table 2.1). The weights are two bytes wide, so a whole memory cache line can hold  $16l_{RDC}/2$  weights or  $\alpha = 8l_{RDC}/n_{v2}$  rows of weights.

Loading a matrix stripe of 64 columns, the memory cache line has to be updated  $n_{p1}/\alpha$  times; and there are  $\beta$  banks involved per update. The banks are interleaved every 128B respective 64 weights. In the best case,  $n_{p1}/64$  is a multiple of four and all matrix rows start in the same bank ( $\beta = 1$ ). When that number is only a multiple of two, then  $\beta = 2$  banks are involved per cache update, and in every other case even all four banks are involved.

Therefore, there occur  $2\beta n_{p1}/\alpha$  memory cache misses, when loading 64 matrix columns. Only half of these misses can be seen, because one vector load uses two memory ports and two loads can be overlapped. All the other weight accesses are hits. The memory has only two cache lines, and all the memory accesses during the forward step are reads. For these reasons only  $\max(2\beta, \beta n_{p1}/\alpha)$  cache misses can have a dirty cache line.

#### Run time of the matrix vector multiplication

Some weight vectors can be loaded from the RDRAM caches, others are directly loaded from the RDRAM. A load hit takes only 14 cycles and its run time is dominated by the 16 cycle computation time. A load miss, however, takes between 22 and 28 cycles and dominates the computation time. A detailed analysis of the assembler code (Appendix A.1) therefore yields the following run time for one pass of the matrix vector multiplication code:

$$\begin{split} T_{MVM} &= r_{m,d} + (n_{p1} - 2) \max(16, r_h) + 20 \\ &+ \beta \frac{n_{p1}}{\alpha} (r_{m,/d} - 16) + \min\left(2\beta - 1, \beta \frac{n_{p1}}{\alpha} - 1\right) (r_{m,d} - r_{m,/d}) \\ &= r_{m,d} + 16n_{p1} - 12 \\ &+ \frac{\beta n_{p1} n_{p2}}{8l_{RDC}} (r_{m,/d} - 16) + \min\left(2\beta - 1, \frac{\beta n_{p1} n_{p2}}{8l_{RDC}} - 1\right) (r_{m,d} - r_{m,/d}) \end{split}$$

|            | 128                                                                     | Nodes                                                                        | 1024 Nodes                                                              |                                                                                         |  |

|------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| p          | $p_i = 8$                                                               | $p_h = 16$                                                                   | $p_i = 16$                                                              | $p_h = 64$                                                                              |  |

| Processor  | every $4^{th}$ node                                                     | 4 columns, 4                                                                 | every $2^{nd}$ node                                                     | 2 columns, 32                                                                           |  |

| Subnet     | per row                                                                 | nodes each                                                                   | per row                                                                 | nodes each                                                                              |  |

| $T_{gsum}$ | $\begin{array}{c} \sum_{i=2}^{4} T_{MT}(2^i) \\ +20 \log p \end{array}$ | $\begin{array}{c} \sum_{i=0}^{1} 2  T_{MT}(2^{i}) \\ +20 \log p \end{array}$ | $\begin{array}{c} \sum_{i=1}^{4} T_{MT}(2^i) \\ +20 \log p \end{array}$ | $\begin{array}{c} \sum_{i=0}^{4} T_{MT}(2^{i}) \\ +T_{MT}(1) \\ +20 \log p \end{array}$ |  |

|            | $28 m_{length} +$                                                       | $6 m_{length} +$                                                             | $30 \; m_{length} +$                                                    | $32  m_{length} +$                                                                      |  |

|            | $56 + 59 \log p$                                                        | $12 + 59 \log p$                                                             | $60 + 59 \log p$                                                        | $64 + 59 \log p$                                                                        |  |

|            | Step 2                                                                  | Step 3                                                                       | Step 2                                                                  | Step 3                                                                                  |  |

Table 4.6: Run time for global sum [cc]

In our investigation  $n_{p1}$  is a power of two and at least 512, therefore  $\beta = 1$ .

#### 4.2.2 Global sum

The four global sums are executed by messages handlers. One handler computes the direction of the message and sends the vector Rt; the other handler receives a vector and adds it to the register Rt. We assume that this administrative overhead takes about 20 cycles.

Let p be the number of processors which share the same result vector in steps 2 or 3; then a global sum is executed in  $\log p$  iterations. The run time of one iteration depends on the size of the CNS and the distribution of the matrices. The different cases are listed in Table 4.6.

#### 4.2.3 Sigmoid computation

The four sum vectors are still in the vector registers, but the data have the wrong format. That is corrected by shift and clip instructions. The sigmoid table is stored in main memory, but after the preload step the whole table is present in the RDRAM caches. Nevertheless, a table access still needs more time than an arithmetical operation and a D-cache access. For that reason the sigmoid computation of four vectors takes time  $T_{sig} = T_{preload} + 4T_{table} + 4$ ; 4 cycles are necessary for storing the last result vector in the D-cache. The preload and table access times depend on the size of the sigmoid table and the access patterns. The table has 16K or 32K elements. The access patterns depend on the inputs, and even under the assumption that all accesses are spread equally over the whole table, we have to analyze the best and the worst case.

#### Memory analysis

**4.5Mb memory chip** Each of the 16 memory chips has two 1KB cache lines. The 16K table therefore fits in one cache line, while the 32K table occupies two lines. One vector word access is sufficient to load a cache line of a memory bank. So a preload of 16K data

takes 4(152 + 64) ns or  $T_{preload} = 4 \cdot 27 = 108$  cycles. Preloading the larger sigmoid table takes 216 cycles, twice the time  $T_{preload}$ .

After the preload, each table access is a hit, and the table access time only depends on the access pattern. In the best case all 32 requests are equally distributed over the memory ports, then four request can be overlapped. At worst, all requests use the same memory port and have to be executed sequentially. It takes (48+2) ns or 7 cycles to load one byte from the memory cache. The table access for four vectors takes in that case:

$$4 T_{table} = \begin{cases} 4 \cdot \frac{32}{4} \cdot 7cc + 3cc &= 227cc \\ 4 \cdot 32 \cdot 7cc &= 896cc \end{cases}$$

best case worst case.

18Mb memory chip The analysis is almost the same as in the previous case, but now the cache line is twice as large. Even a table with 32K elements fits in a single cache line and can be loaded in four steps. The memory is also slightly faster. A preload takes only 4(112+64) ns or 88 cycles. This time is based on a clean cache miss. That is realistic because the processors do not write into the main memory during steps 2 and 3. It takes (44+2) ns or 6 cycles to load a byte from the memory cache. The table lookups of four vectors can now be done in the time:

$$4 T_{table} = \begin{cases} 4 \cdot \frac{32}{4} \cdot 6cc + 3cc &= 195cc \\ 4 \cdot 32 \cdot 6cc &= 768cc \end{cases}$$

best case worst case.

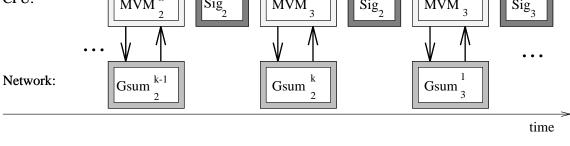

#### 4.2.4 Interleaving the three main routines

Global sum is the only routine with network traffic, and its code is executed in message handlers. For these reasons the four global sums can run in parallel with the next matrix vector multiplication. From time to time the handlers interrupt the multiplication, but only  $8 \log p$  times.

It is better not to interrupt the sigmoid computation, because an interrupt could cause an I-cache miss which swaps the sigmoid table out of the memory cache. Afterwards it takes up to four memory accesses to load the table again. It should be possible to avoid these undesirable interrupts by scheduling the sigmoid computation as a high priority thread. Figure 4.1 shows the execution scheme of steps 2 and 3.

There occurs some overhead in the forward step. The processors handle two procedures, and three threads per pass of the outer loop. One procedure handling takes time  $T_{proc}$  and the handling of a thread time  $T_{thr}$ . The nodes also have to load five parameters per procedure. Only the first load instruction is a memory cache miss. In the small memory system it takes  $t_{par} = (20 + 4 \cdot 7) = 48$  cycles to load five words; the large system needs  $t_{par} = (21 + 4 \cdot 7) = 49$  cycles. The following formula therefore describes the run time of steps 2 and 3:

$$T_{step2,3} = T_{MVM}(n_{pi}, n_{ph}) + \left(\frac{n_{ph}}{64} - 1\right) \max \left(T_{MVM}(n_{pi}, n_{ph}) + 40 \log p_i, 4T_{Gsum}(p_i)\right)$$

$$+ \frac{n_{ph}}{64} T_{Sig} + \max \left(T_{MVM}(n_{ph}, n_{po}) + 40 \log p_i, 4T_{Gsum}(p_i)\right)$$

$$+ \left(\frac{n_{po}}{64} - 1\right) \max \left(T_{MVM}(n_{ph}, n_{po}) + 40 \log p_h, 4T_{Gsum}(p_h)\right) + \frac{n_{po}}{64} T_{Sig}$$

$$+ 4T_{Gsum}(p_h) + 2T_{proc} + 2 \cdot t_{par} + 3\frac{n_{ph} + n_{po}}{64}T_{thr}.$$

#### 4.2.5 Penalty of I-cache misses

The I-cache is organized in 32 blocks with 32 instructions each. The sigmoid computation needs less than 32 instructions, and the matrix vector multiplication fits in five blocks or fewer. The send handler of global sum is coded in two blocks and the receive handler in one block. Steps 2 and 3 have almost the same code, only the send handlers are different. All together the code needs twelve blocks or fewer and should fit in the I-cache, but a bad mapping can avoid that.

At worst, all routines have to share the same cache line. That causes a lot of I-cache misses. One miss stalls the machine up to 44 cycles and can also influence later data accesses.

#### Amount of I-cache misses

The processors load the code of the matrix vector multiplication during the first iteration of step 2, that causes five I-cache misses. Only one of them is dirty because the code fits in one memory cache line and there are no memory writes in our version of the forward step.

In later iterations, the global sum message handlers interrupt the matrix vector multiplication. Both handlers together have three blocks of code; that means three misses per two interrupts. The two blocks sigmoid code cause two misses per iteration. At worst, the multiplication code has to be restored after each iterupt. That doubles the misses, caused by message handlers and sigmoid computation. The last iteration of step 3 is different. The message handlers and the sigmoid code do not share the cache with the multiplication, so there is no restoring and the message handlers are resident in the cache during the whole global sum computation. The following formula describes the amounts of I-cache misses  $N_{Im}$  during steps 2 and 3, each miss stalls the CPU up to 44 cycles:

$$N_{Im} = 5 + \frac{n_{ph}}{64} \cdot 2 \cdot (12 \log p_i + 2) + \left(\frac{n_{po}}{64} - 1\right) \cdot 2 \cdot (12 \log p_h + 2) + 3 + 2$$

$$= 6 + \frac{n_{ph}}{64} \cdot (24 \log p_i + 4) + \frac{n_{po}}{64} \cdot (24 \log p_h + 4) - 24 \log p_h.$$

#### Influence on data accesses

Loading a block of instructions destroys a cache line of a whole memory bank, the old data are gone. The next access to these data therefore causes a clean memory cache miss. Those misses occur during the matrix vector multiplication and the sigmoid computation.

Matrix vector multiplication During the matrix vector multiplication the vectors are loaded in half word mode; the execution of two vector loads is overlapped. It therefore takes two accesses to restore the RDRAM cache again, but only one of the misses can be seen.

The amount of swapped cache lines influencing the data accesses of the matrix vector multiplications can be derived from the total amount of I-cache misses  $N_{IM}$ . Misses occurring in the message handlers and in the sigmoid computation have no direct influence, only

| RDRAM   | Table Access            | Pattern           |

|---------|-------------------------|-------------------|

| Version | Best Case               | Worst Case        |

| 4.5 Mb  | $1 \cdot (20 - 7) = 13$ | $4 \cdot 13 = 52$ |

| 18 Mb   | $1 \cdot (15 - 6) = 9$  | $4 \cdot 9 = 36$  |

Table 4.7: Delay of the table lookup time of four vectors caused by I-cache misses [cc]

restoring the multiplication code causes significant misses. For these reasons the amount of cache lines containing weight vectors and being swapped by I-cache misses are not higher than

$$\begin{split} N_{Im}(MVM) &= 4 + \frac{n_{ph}}{64} \cdot (12\log p_i + 2) + \left(\frac{n_{po}}{64} - 1\right) \cdot (12\log p_h + 2) \\ &= 2 + \frac{n_{ph}}{64} \cdot (12\log p_i + 2) + \frac{n_{po}}{64} \cdot (12\log p_h + 2) - 12\log p_h. \end{split}$$

At worst, each of the swapped weight vectors replaces a cache hit by a cache miss and extends the data access times by

$$\max(16, r_{m,/d}) - \max(16, r_h) = r_{m,/d} - 16$$

cycles;  $r_h = 14cc, r_{m,/d} \ge 22cc$ .

**Sigmoid computation** The processors load two blocks of sigmoid code during one iteration, but only the second access occurs after the preload of the sigmoid table. At worst, that I-cache miss swaps parts of the sigmoid table out of the RDRAM cache. Accessing and restoring the table then causes up to  $t_{res}$  visible data misses in the RDRAM caches. Each byte access only restores the cache line of a single memory chip.

The best access pattern enables the CPU to schedule requests to all four memory ports at a time; then the table can be restored with one table lookup ( $t_{res} = 1$ ). At worst, no memory accesses can be overlapped and the reload of the table takes up to four requests ( $t_{res} = 4$ ). Table 4.7 shows how these facts influence the table lookup time for different memory systems.

In the second and third step the penalty caused by I-cache misses can be at most  $P_{enalty}$  cycles;

$$P_{enalty} = 44 \cdot N_{Im} + (r_{m,/d}(32B) - 16) \cdot N_{Im}(MVM) + (r_{m,/d}(1B) - r_h(1B)) \cdot t_{res} \cdot \frac{n_{ph} + n_{po}}{64}.$$

#### 4.3 Step 4: Writing the results

This step runs on I/O nodes and processing nodes. All processing nodes save their results in the main memory; and in addition to that the Torrents in the bottom ring send the results

to the attached I/O nodes. Some Hydrants send the results to the outside world; in our case every fourth node. Before that transfer, they collect the data from their neighbors.

The timing of the Hydrants depends on the distribution of the result vectors. We therefore have to analyze the run time for 128 and 1024 nodes. In the Torrent network the run time of step 4 is independent of the machine size.

#### 4.3.1 Timing in the Torrent network

We only analyze the timing of the processors in the bottom ring, because they have the longest run time. Besides saving the results in the main memory they also have to send the data to an I/O node. That transfer takes time  $T_{ST}(1)$ , and further transfers can be started every  $m_{length}+1$  cycle. Each of the  $2 \cdot n_{po}/128$  messages blocks the CPU only for 10 cycles. In the remaining time the CPU saves the results. The vectors are already in vector registers, and storing one vector register takes 44+23=67 cycles at the most, even with a dirty data miss in the small RDRAM and an I-cache miss. The CPU has more than  $m_{length}-9$  cycles per vector and therefore can hide the storing completly behind the transfer.

The message handler and the code of step 4 fit in one cache block each. At worst, they require the same block in the I-cache. That slows the execution down by  $44/64 \cdot n_{po}$  cycles. That yields

$$T_{step4} = \frac{n_{po}}{64}(m_{length} + 1) + 41$$

$$P_{enalty} \leq \frac{11n_{po}}{8}.$$

#### 4.3.2 Timing in the Hydrant network

The distribution of the activations and results is the same, so we can take the same mapping of the Hydrants as for step 1.

The worst case occurs in the 128-machine, because only two columns share the same results there. This implies that  $H_b$  has to get some data from  $H_c$  and send both vectors to the outside world. In the 1024-node machine four columns share the same results, and no transfer occurs between  $H_c$  and  $H_c$ .

#### I/O on the 128-node machine

Messages from the Torrents arrive every  $m_{length}+1$  cycle and block the Hydrant processor and network interface for 10 cycles each. Node  $H_c$  therefore has  $m_{length}-9=128$  cycles to send a message to  $H_b$ , and  $H_b$  has the same amount of time for receiving these data and writing both vectors. Analog to reading, one vector can be written in 20 cycles. Even with an I-cache miss that still fits in 128 cycles. The Hydrant nodes therefore can consume the results at the same speed as the Torrents send them.

#### 4.4 Problems with the D-cache size

Till now we assumed that the local input, hidden and output vectors have 1K elements at most, and so all the local vectors required during one step could be stored in the D-cache.

For some of the systems mentioned in table 3.1 this is not feasible. In this section we analyze how those cache conflicts influence the code and the run time.

#### 4.4.1 Steps 1 and 4

The run time of step 1 mostly depends on the time required for broadcasting the inputs from the Hydrants to the Torrents, as shown in previous analyses (section 4.1). The Torrents receive data, store them in the cache and main memory, and execute some loop overhead. The time they spent in the CPU and the memory system gets only visible when storing the last vector. In the case that the activation vectors are too large for the D-cache the cache accesses can be omitted. That speeds up the last iteration of step 1 by four cycles.

When entering step 4, the output vectors are already stored in the main memory, so only the processors in the bottom ring have to do some work. Originally these Torrents sent the data to the I/O nodes and stored them in the main memory. The memory accesses could completely be hidden behind the transfer. Now they first have to load the vectors before sending them to the Hydrants. Exept for the first load, all memory accesses can still be hidden behind transfer. The first load of 32 words is very likely to be a dirty RDRAM cache miss. The run time of step 4 therefore takes 27 or 28 cycles longer depending on the RDRAM type.

#### 4.4.2 Steps 2 and 3

For step 2 there are two cases which can produce D-cache problems: the hidden vectors or the activation vectors are too large. We will analyze both cases.

#### Too large hidden vectors

The hidden vectors can not be stored in the D-cache, because that would swap the activations out of the cache, but in this step activations are accessed much more often than hidden elements. We therefore keep the activations in the D-cache and store the hidden vectors directly in the main memory.

The hidden vectors are stored at the end of the sigmoid computation, so the additional transfer will not disturb the table lookups. At worst, the store operations cause a drity RDRAM cache miss, but the hidden vectors are only one byte wide, and so the four writes can be overlapped. When using the small RDRAM, four vectors can be stored in 23+3\*4=35 cycles. The large RDRAM is one cycles faster. The sigmoid computation of four vectors takes now

$$T_{Sig} = T_{preload} + 4T_{table} + 4 + \begin{cases} 35 & ; 4.5 \text{ Mbit RDRAM chips} \\ 34 & ; 18 \text{ Mbit RDRAM chips}. \end{cases}$$

This D-cache problem only influences the sigmoid computation.

#### Too large activation vectors

We still keep as many activations in the D-cache as possible. This implies that even very small hidden vectors have to be stored directly in the main memory. We already analyzed in

Table 4.8: Pseudocode of the matrix vector multiplication. The two input vectors with length np1 are too large for the D-cache, so they are loaded in blocks of 1KB.

the previous paragraph, how this influences the sigmoid execution time. The D-cache is too small to store the local parts of both activation vectors at the same time. The processors therefore only load chunks of one kilo byte in the cache. Table 4.8 shows the new pseudocode for the matrix vector multiplication. Variables starting with C, R or r indicate that these data will be stored in the on-chip D-cache, the vector registers or the scalar registers.

The mapping of the activation vectors requires some attention. The two activation vectors should be stored close together in the main memory to minimize the amount of RDAM cache misses. On the other hand, it should also be possible to keep korresponding parts of both vectors in the D-cache. The mapping therefore has to prevend, that corresponding parts allocate the same space in the D-cache. At worst, there are 1KB data between the two vectors.

The only difference between the new and the original code (table 4.4) is the blocktransfer of the activations. When transfering the data in word mode, the four memory ports can work in parallel. The four memory banks per port will only cause four misses, because both activation vectors completely fit into one memory cache line. The size of the memory cache line is  $16l_{RDC}$ , that is  $16\mathrm{KB}$  or  $32\mathrm{KB}$ . In our analysis, the local vectors will be at most 4096 elements. The transfer of a  $1\mathrm{KB}$  block of both vectors takes

$$4r_{m,d} + \left(\frac{2 \cdot 1024}{4 \cdot 32} - 4\right)r_h = 4r_{m,d} + 12r_h$$

cycles, using the notation of table 4.5. There occurs  $n_{p1}/1024 = n_{pi}/1024$  of these block-transfers per pass through the outer loop of the matix vector multiplication

These transfers do not influence the matrix access time. One memory cache line can only keep less that eight matrix rows. So after 1024 rows the matrix access would be a

RDARM cache miss even without the blocktransfer. These cache problems slow the matix vector multiplication down by about 1.5%, as the new run time formular shows.

$$\begin{split} T_{MVM}(n_{p1} \geq 2K) &= \frac{n_{p1}}{1024} (4r_{m,d} + 12r_h) + T_{MVM} \\ &= \frac{n_{p1}}{1024} (4r_{m,d} + 12r_h) + r_{m,d} + 16n_{p1} - 12 + \\ &= \frac{\beta n_{p1} n_{p2}}{8l_{RDC}} (r_{m,/d} - 16) + \min\left(2\beta - 1, \frac{\beta n_{p1} n_{p2}}{8l_{RDC}} - 1\right) (r_{m,d} - r_{m,/d}) \\ &= \text{where } \beta = 1, \, n_{p1} = n_{pi} \text{ and } n_{p2} = n_{ph} \end{split}$$

#### Step 3

In this step we have a similar situation than in step 2, so the same analysis can be used. The hidden vectors now play the role of the input vectors and the output vectors play the role of the result vectors. This implies that now the cache problems are caused by too large output or hidden vectors.

Besides these two cases there is also a new case. The hidden vector fits in the D-cache, but in step 2 it was written to the main memory because the activation vectors required the whole D-cache. At the beginning of step 3 all processors transfer the hidden vector from the main memory to the D-cache. This transfer is similar to the blocktransfer described earlier and therefore it takes time

$$4r_{m,d} + \left(\frac{2 \cdot n_{ph}}{4 \cdot 32} - 4\right) r_h = 4r_{m,d} + \left(\frac{n_{ph}}{64} - 4\right) r_h.$$

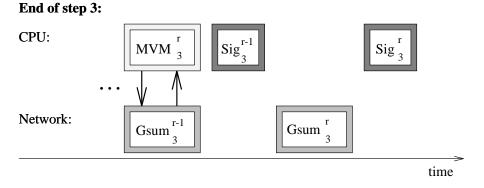

# Beginning of step 2: CPU: $MVM_2^1$ $Sig_2^1$ $MVM_2^2$ $Sig_2^2$ Network: $Gsum_2^1$ $Gsum_2^2$ Switching from step 2 to step 3: CPU: $MVM_2^k$ $Sig_2^{k-1}$ $MVM_3^1$ $Sig_2^k$ $MVM_3^2$ $Sig_3^1$

Figure 4.1: Interleaving scheme of steps 2 and 3. MVM stands for matrix vector multiplication, Sig for sigmoid computation and Gsum for global sum. The lower index indicates the step number, and the upper index counts the iterations. Step 2 is executed in  $k = n_{ph}/64$  iterations and step 3 in  $r = n_{po}/64$  iterations. Arrows between threads indicate that the network thread will interrupt the CPU thread from time to time, to get some computation done.

# Chapter 5

# Performance Results of Kernel 1

In the previous chapter we developed formulas for the run time of kernel 1 under different conditions. In this chapter we determine the CNS performance under those conditions and investigate the results. We also analyze the performance impact of the data distribution and of the parallelization scheme.

#### 5.1 Performance results

To get performance results for different conditions, we vary the number of processing nodes, the RDRAM type, the dimensions of the neural network and the size of the sigmoid lookup table. For other parameters, like the access pattern of the lookup table and the models of memory refesh and of I-cache misses, we consider best and worst cases.

The absolute performance of the CNS running kernel 1 is measured in connection per second [CPS]. The amount of arithmetical operations during recall equals one multiply-accumulate instructions per connection. Each node has a peak performance of 1 GMAS (Giga multiply-accumulate per second). The peak performance for kernel 1 is therefore p GCUPS. Comparing the absolute performance with the peak performance yields the relative performance measured in %.

#### 5.1.1 Detailed results under fixed conditions

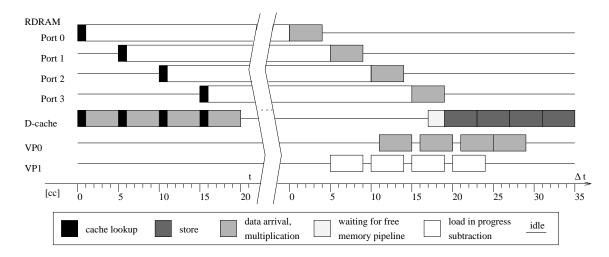

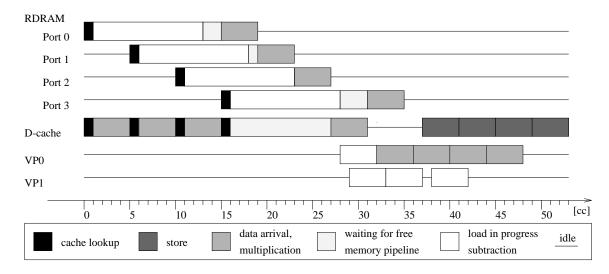

We now investigate the performance of the 128-node machine with 4.5 Mb memory chips on a neural network comprising 192M connections. The net has 8K inputs, 16K hidden units and 4K outputs. Table 3.1 shows the corresponding values for the local problem size and the partitioning of the machine. Steps 1 and 2 are executed in 16 rounds, steps 3 and 4 in only 8 rounds. Inserting these parameters in the run time formula explains how the matrix vector multiplication, the global sum, the sigmoid computation and the I/O influence the run time of kernel 1.

The matrix vector multiplications and the global sums are the most timeconsuming routines, but their execution can partially be overlapped, because the global sums spend most of their time in the processor network. The results in table 5.1 show that the network latency can largely be hidden, at least under the given conditions.

|      | Matrix   | (    | Global Sı |         |       |

|------|----------|------|-----------|---------|-------|

| Step | Vector   | CPU  | Net       | Network |       |

|      | Multiply |      | visible   | hidden  |       |

| 2    | 17807    | 480  | 15796     |         | per   |

| 3    | 17103    | 640  | ć         | 3640    |       |

| 2    | 284912   | 7680 | 0         | 252736  | total |

| 3    | 136824   | 5120 | 3640      | 29120   | ioiai |

Table 5.1: Run time of the matrix vector multiplication and the global sums, based on the best case of I-cache misses ([cc]).

| Sign           | Matrix |      |       |       |          |

|----------------|--------|------|-------|-------|----------|

| Access Pattern | Best   | Case | Worst | Case  | vector   |

| Table Size     | 16K    | 32K  | 16K   | 32K   | Multiply |

| Step 2         | 5424   | 7152 | 16128 | 17856 | 284912   |

| Step 3         | 2712   | 3576 | 8064  | 8928  | 136824   |

Table 5.2: Sigmoid computation time for the best case of I-cache misses ([cc]).

The sigmoid computation time depends on the size of the lookup table and the access patterns. The size of the lookup table has only a 29% impact on the run time, but the access patterns have a much stronger influence. Bad patterns can triple the sigmoid execution time of the best case (table 5.2).

The sigmoid computation contributes less than 7% to the total run time of kernel 1, and therefore changes in the size of the lookup table or in the access patterns become negligible phenomena for the run time of kernel 1. Changing the table size from 16K to 32K only results in a performance loss of less than 0.6% and bad access patterns in a performance loss of 3.5%, at most. I/O and administrative overhead add another 3% to the total run time.

Table 5.3 shows that a major performance penalty is related to I-cache misses. Actually, the code of kernel 1 is small enough to fit in the I-cache, but a bad mapping may cause that all routines have to share the same cache block. That results in a lot of cache misses, most of them related to message handler interrupts. Under the given conditions, such a bad mapping increases the total run time by about 22%.

#### 5.1.2 General results

The previous results show that refresh and changes in the table lookup behavior have virtually no impact on the total performance. For the next analysis we therefore assume the worst case of both parameters.

As already seen before, the performance penalty for I-cache misses is quite high. At worst, these misses increase the run time by 30% (Table 5.4), and so they have a stronger

| Mo             | Run Time [cc] |        |        |      |          |        |

|----------------|---------------|--------|--------|------|----------|--------|

| I-Cache Misses | Table Lookup  | Step 2 | Step 3 | I/O  | Overhead | Total  |

| Best Case      | Best Case     | 298016 | 148296 | 3546 | 9378     | 459222 |

| Dest Case      | Worst Case    | 310448 | 154512 | 3546 | 9378     | 477870 |

| Worst Case     | Best Case     | 358680 | 183314 | 7462 | 9378     | 558820 |

| Worst Case     | Worst Case    | 371736 | 189842 | 7462 | 9378     | 578404 |

Table 5.3: Run time of kernel 1.

| RDRAM  | Connections |          |                 |      |       |  |  |  |

|--------|-------------|----------|-----------------|------|-------|--|--|--|

| Chips  | 192M        | 768M     | 1536M           | 768M | 1536M |  |  |  |

| 4.5 Mb | 21.7        | 10.8     | 7.9             | 28.9 | 27.8  |  |  |  |

| 18 Mb  | 21.3        | 10.8     | 8.2             | 27.7 | 27.0  |  |  |  |

|        | 128         | 8 Proces | 1024 Processors |      |       |  |  |  |

Table 5.4: Worst case penalty of I-cache misses [%]